面向 21 世纪 课 程 教 材

Textbook Series for 21st Century

# 数字电子技术基础

(第六版)

清华大学电子学教研组 编

主 编 阎石

修订者 阎石 王红

高等教育出版社

面向 21 世 纪 课 程 教 材

Textbook Series for 21st Century

公众号：奶啤软件百货

# 数字电子技术基础

SHUZI DIANZI JISHU JICHU

(第六版)

清华大学电子学教研组 编

主 编 阎石

修订者 阎石 王红

高等教育出版社·北京

# 公众号：奶啤软件百货

## 内容简介

本书是为高等学校开设数字电子技术基础课程编写的教材。书中全面、系统地介绍了数字电子技术的基础知识。新版教材是在原书第五版的基础上修订而成的。

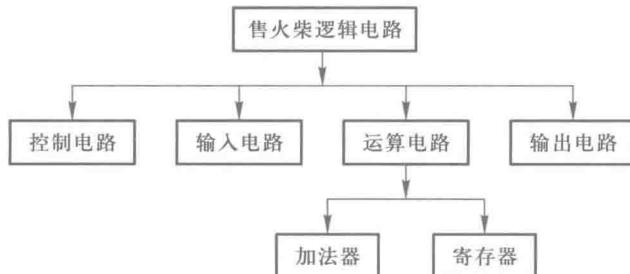

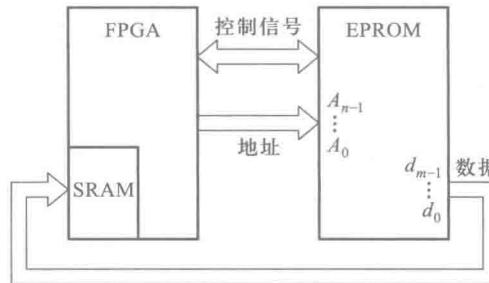

全书由数制和码制、逻辑代数基础、门电路、组合逻辑电路、半导体存储电路、时序逻辑电路、脉冲波形的产生和整形电路、数—模和模—数转换等八章和附录组成。在修订后的教材里，将原来可编程逻辑器件和硬件描述语言两章的内容纳入到了组合逻辑电路和附录当中。同时，在各章中还配有丰富的例题、思考题和习题。

本书自第一版发行以来，经历了五次修订。其中第二版获国家教委优秀教材一等奖，第三版获国家优秀教材奖，第四版获北京市高等教育教学成果一等奖，第五版获北京市精品教材奖并被评为北京高等教育经典教材。

本书可作为高等院校电气类、电子信息类、自动化类、仪器仪表类各专业的教材，也可供其他理工科专业选用或供社会读者阅读。

## 图书在版编目(CIP)数据

数字电子技术基础/阎石,王红编;清华大学电子学教研组编. -- 6 版. -- 北京:高等教育出版社,

2016.4

ISBN 978 - 7 - 04 - 044493 - 3

I. ①数… II. ①阎… ②王… ③清… III. ①数字电路-电子技术-高等学校-教材 IV. ①TN79

中国版本图书馆 CIP 数据核字(2015)第 308741 号

策划编辑 欧阳舟

责任编辑 韩 颖

封面设计 李卫青

版式设计 童 丹

插图绘制 黄建英

责任校对 刘娟娟

责任印制 朱学忠

出版发行 高等教育出版社

网 址 <http://www.hep.edu.cn>

社 址 北京市西城区德外大街 4 号

<http://www.hep.com.cn>

邮政编码 100120

<http://www.hepmall.com.cn>

印 刷 高教社(天津)印务有限公司

<http://www.hepmall.com>

开 本 787mm×1092mm 1/16

<http://www.hepmall.cn>

印 张 31.75

版 次 1981 年 7 月第 1 版

字 数 770 千字

2016 年 4 月第 6 版

购书热线 010 - 58581118

印 次 2016 年 4 月第 1 次印刷

咨询电话 400 - 810 - 0598

定 价 49.30 元

本书如有缺页、倒页、脱页等质量问题，请到所购图书销售部门联系调换

版权所有 侵权必究

物 料 号 44493 - 00

## 作 者 声 明

未经本书作者和高等教育出版社许可,任何单位和个人均不得以任何形式将《数字电子技术基础》(第六版)中的习题解答后出版,不得翻印或在出版物中选编、摘录本书的内容;否则,将依照《中华人民共和国著作权法》追究法律责任。

## 第六版前言

《数字电子技术基础》第六版是在原书第五版的基础上修订而成的。为了适应数字电子技术的不断发展和应用水平的不断提高，主要从以下几方面对原教材作了修订。

一、在基本保持原有理论体系的情况下，对体系结构作了较大调整。将原来“触发器”和“半导体存储器”两章的主要内容合并为现在的“第五章 半导体存储电路”，同时取消了原有的“可编程逻辑器件”和“硬件描述语言”两章。这样就将原来十一章的内容整合成了现在的八章。

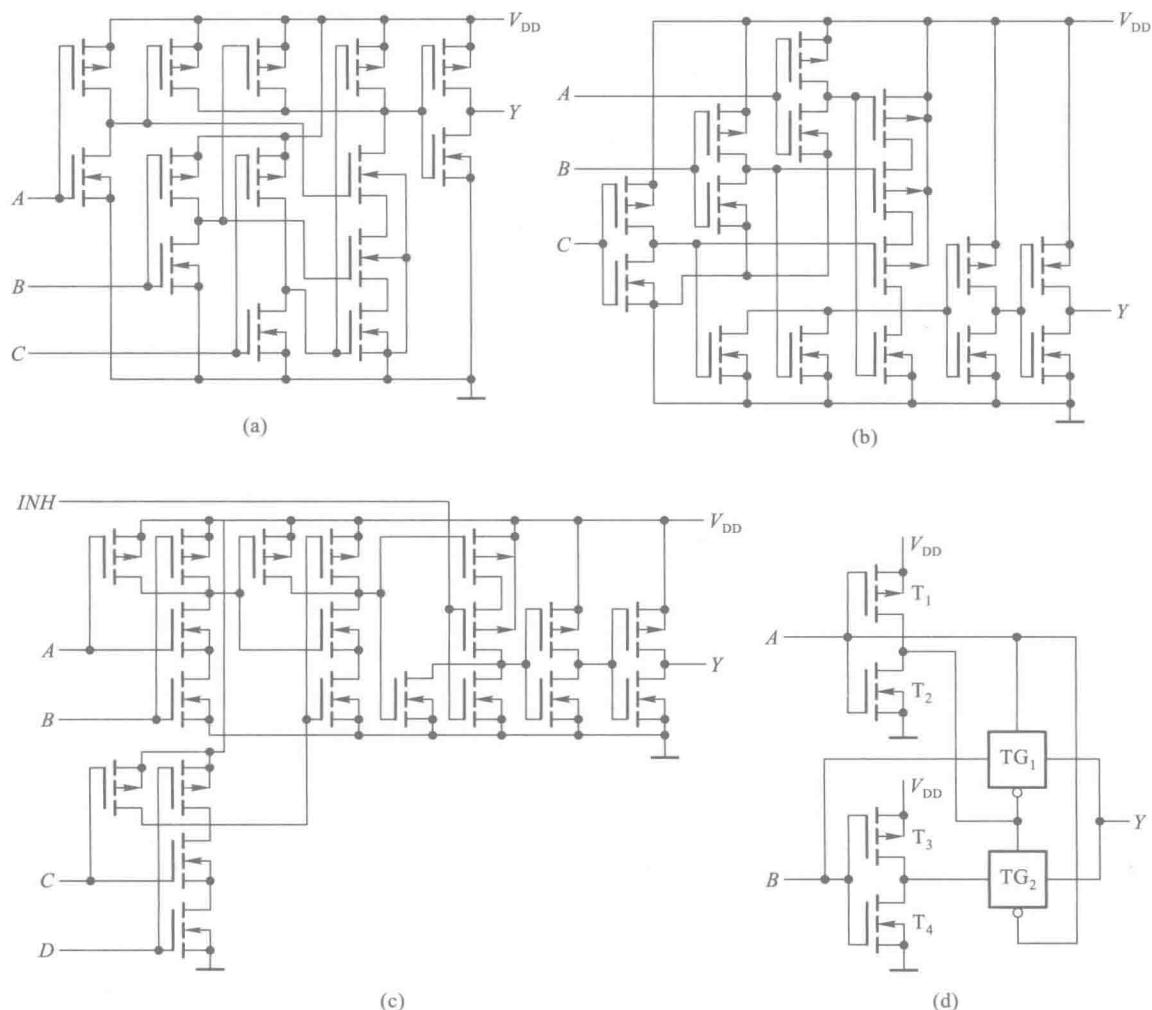

二、大幅度地压缩和删减了对集成电路内部结构的详细介绍，以及某些不重要的或者陈旧的内容，例如触发器电路结构中一些不常见的类型、存储电路中各种双极型存储单元、 $I^2L$  电路、各种 PLD 器件内部结构的详细介绍、Multisim 的使用等。

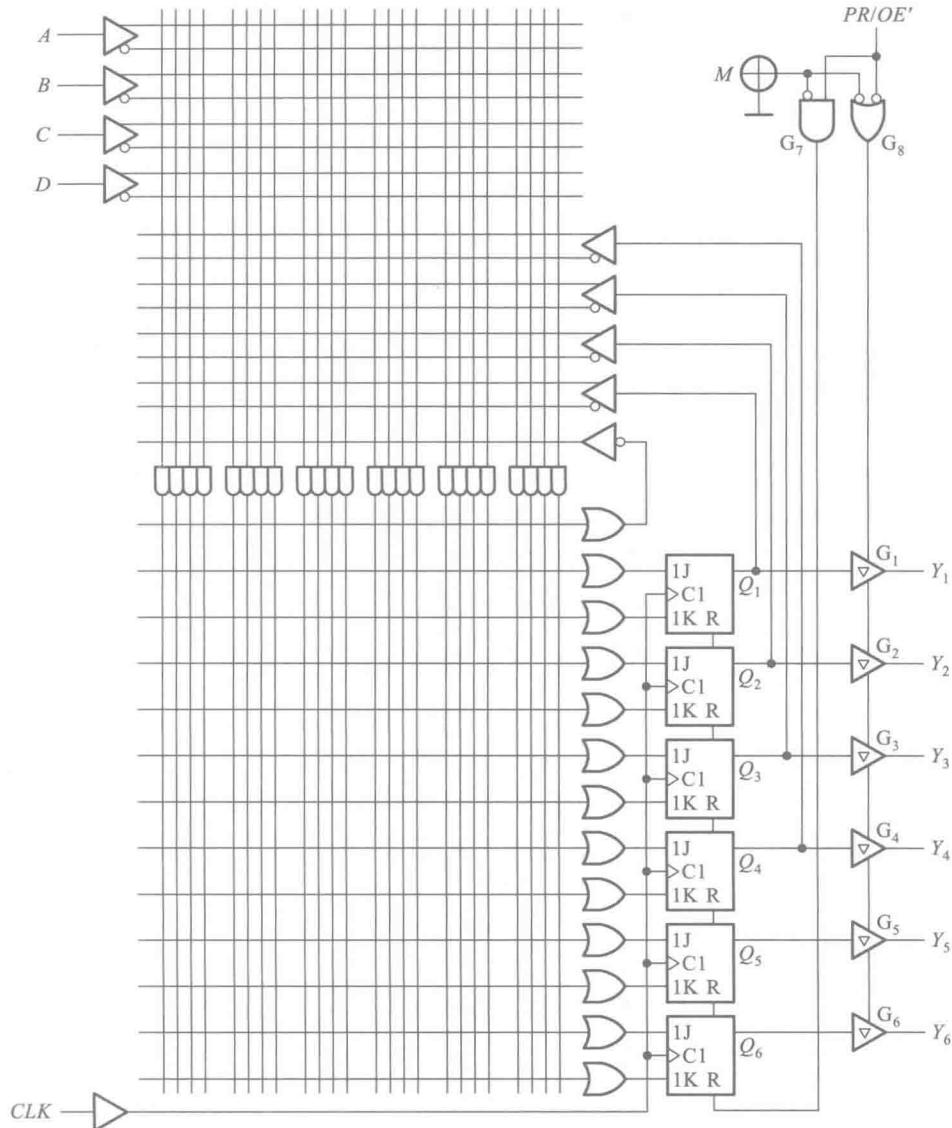

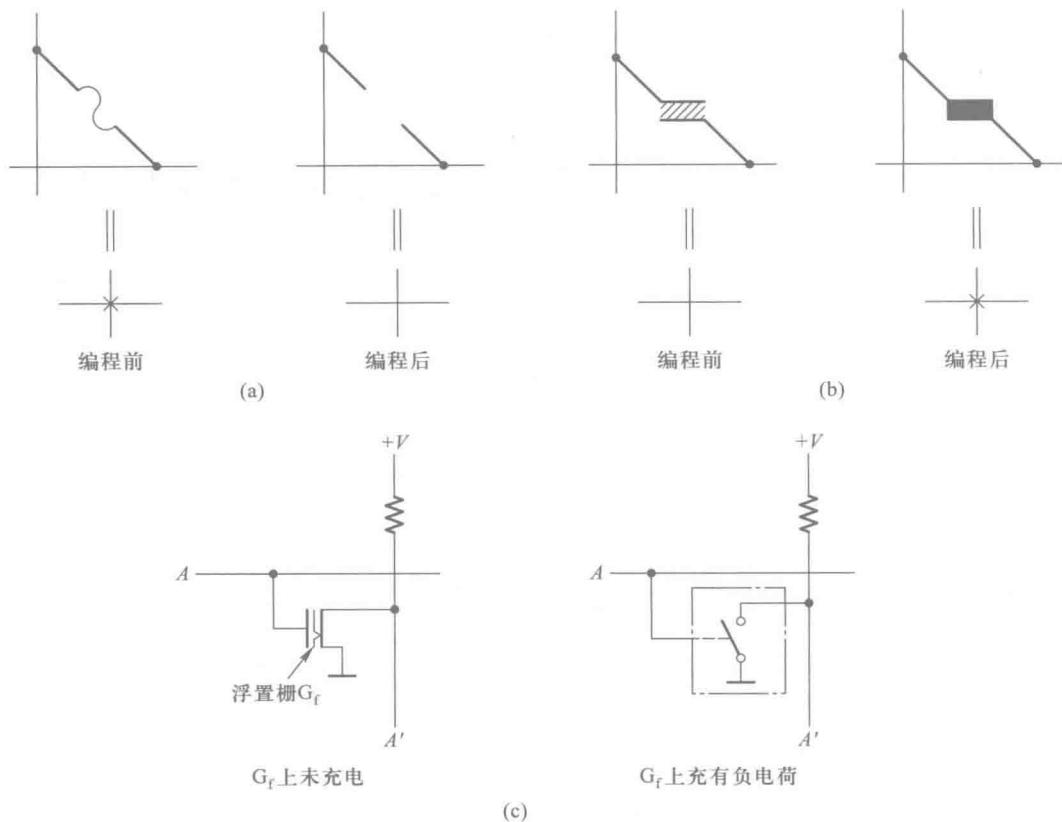

PLD 最主要的特点在于它的“可编程”特性。鉴于其内部包含的各种基本逻辑单元、各种逻辑模块电路以及可编程互联单元等在其他章节中均有详细介绍，所以把 PLD 可以看作是一种规模更大的通用逻辑模块电路，既可以用它作组合逻辑电路的通用模块使用，也可用作时序逻辑电路的通用模块使用。因此，在组合逻辑电路和时序逻辑电路中引入 PLD 作为可编程的通用逻辑模块以后，就不再将 PLD 的内容单独写成一章了。而且，PLD 作为一种工业产品，不仅种类和型号繁杂，而且还在不断升级换代。因此，对各种类型 PLD 器件的内部电路结构逐一作详细介绍就显得不十分重要了。

在第四章中引入 PLD 的同时，也引进了硬件描述语言的基本概念。目前常用的硬件描述语言无论是 VHDL 还是 Verilog，都有全面、严格的话语和规定，本书中不可能作全面、系统的详细介绍。需要深入了解和使用这些硬件描述语言时，可以参阅有关书籍或登录相关网站获取所需资料。为此，在修订后的教材中就不再将硬件描述语言的介绍单列为一章了。

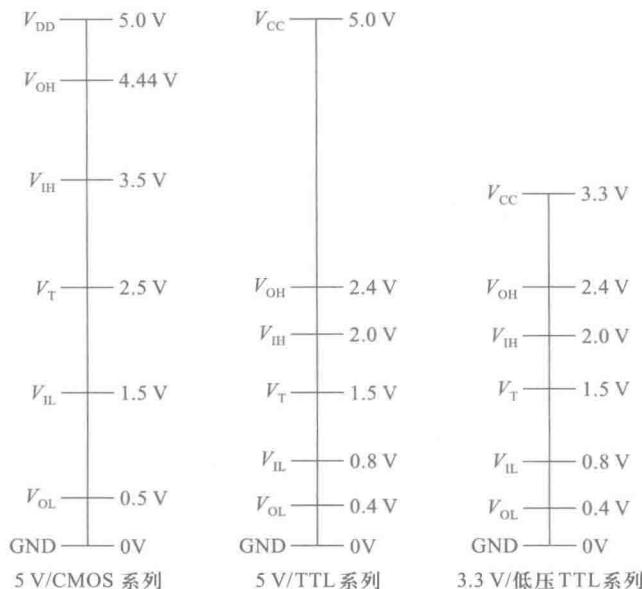

三、根据目前数字电子技术的发展和应用情况，适量地补充了部分内容。其中包括第八章中的流水线型 A/D 转换器、 $\Sigma-\Delta$  型 A/D 转换器、第五章中的动态存储器工作原理、第三章中低压 CMOS 系列的介绍等。

四、在脉冲产生和整形电路中，有些多年沿用的电路名称不甚合理，容易引起概念混淆。在本次修订过程中，对这些电路名称作了调整。例如“施密特触发器”、“单稳态触发器”中都含有“触发器”字样，而“触发器”一词已经在存储电路中作为双稳态存储单元电路的名称使用了。“施密特触发器”、“单稳态触发器”和“触发器”不仅各具有不同的工作特性，而且它们的英文名称原本就不同。在修订后的教材中，只将双稳态存储单元电路叫做“触发器”，而在其他电路名称中将不再出现“触发器”字样。

本次修订工作中，第四章和第六章的修订由王红完成，阎石负责其余部分的修订和全书的统

稿工作。北京大学王志军教授不辞辛劳地仔细审阅了全部书稿，并提出了许多宝贵的意见和建议，谨向他致以最诚挚的谢意。同时，也向所有支持和帮助本书修订出版工作的同志们表示衷心感谢。

修订后的教材中难免还有疏漏、不妥、甚至错误之处，恳求读者给予批评指正。

阎 石

2014 年 10 月

## 第一版前言

---

这套教材是参照高等学校工科基础课电工、无线电类教材会议在1977年11月制定的“电子技术基础”(自动化类)编写大纲和各兄弟院校后来对该大纲提出的修改意见编写的,以《模拟电子技术基础》和《数字电子技术基础》两书出版。本书是其数字电子技术基础部分。全书共有九章,分为上、下两册。上册包括门电路、数字电路的逻辑分析、组合逻辑电路、时序逻辑电路及脉冲波形的产生和整形等五章。这是数字电路的基本部分。下册包括金属-氧化物-半导体集成电路、数模和模数转换、数字电路中的若干实际问题以及综合读图练习等四章,作为选讲部分。在安排教学内容时,可以视具体要求和学时的多少,作必要的增删。

在处理不断出现的新器件和基本内容的矛盾时,我们采取的措施是:以小规模和中规模集成电路为主来组织内容,并适当介绍大规模集成电路;而在基本数字脉冲单元方面,则仍以分立元件为主。

考虑到目前的数字电子技术课程多半安排在模拟电子技术课程之后,所以在用到模拟电路中的有关内容时,就直接作为结论加以引用了。

本书是由清华大学电子学教研组的同志们集体编写的,其中第一章由金国芬、阎石执笔,第二章由余孟尝执笔,第三章由赵佩芹执笔,第四、六章由许道荣执笔,第五章由李大义执笔,第七章由周明德执笔,第八章由吴年予执笔,第九章由赵佩芹、张乃国执笔,阎石同志担任主编。全部编写工作都是在教研组主任童诗白教授亲自组织与具体指导下完成的。

在本教材的整理和定稿过程中,承许多兄弟院校的老师对征求意见稿提出宝贵意见。审稿会上,在主审单位西安交通大学沈尚贤教授的主持下,华中工学院、南京工学院、浙江大学、山东工学院、昆明工学院、东北工学院、合肥工业大学、贵州工学院、上海交通大学、天津大学、华北电力学院、哈尔滨工业大学、吉林工业大学、大连工学院、重庆大学、湖南大学、太原工学院、华南工学院、同济大学、成都科技大学等兄弟院校的老师们仔细阅读了原稿,指出许多错误和欠妥之处。在评审和复审过程中,又经沈尚贤教授和西安交通大学电子学教研室胡瑞雯、林雪亮、古新生等同志写出详细的修改意见,在此谨致以诚挚的谢意。

由于我们对先进的数字电子技术了解不够,本教材又缺乏一定的教学实践,虽然已经根据兄弟院校老师们的意見对征求意见稿作了修改,但必然还存在不少缺点和错误,殷切期望各方面的读者能给予批评和指正。

编 者

1981年1月

公众号：奶啤软件百货

## 第二版说明

---

本书原分上、下两册出版。考虑到教学上的方便，同时考虑到第八章（电子电路中元器件的选择和抗干扰问题）和第九章（数字电路应用举例）的内容不在教学大纲的要求之内，因此决定将第一至第七章及附录合印成一册出版。

编 者

1984年9月

## 第三版序

---

自《数字电子技术基础》(第一版)出版至今,已经过去七年了。由于电子技术及其应用又有了很大的发展,同时国家教育委员会主持制定了电子技术基础课程的教学基本要求,因而对原书进行全面的修订就势在必行了。

修订工作主要是针对以下几个方面进行的:

从内容上,进一步削减了分立元件电路和讲述集成电路内部结构及其详细工作过程的内容,增强了CMOS电路和中、大规模集成电路应用的比重。同时,还适当介绍了一些近年来迅速发展起来的新型器件和电路,如高速CMOS电路、半定制集成电路等。

鉴于原书中各章的习题与内容配合得不够紧密,而且新版教材的内容又改动很大,所以这次更换了绝大部分的习题。另外,为便于读者自行检查学习效果,每章除思考题与习题之外还增加了自我检验题,并在全书的最后给出了这些题目的答案。自我检验题所涉及的内容都是各章的基本概念、基本原理和基本的分析、设计方法。

从体系上,在基本沿用原书体系的基础上,作了一些局部调整。首先调换了第一、二章的先后次序。因为门电路一章的分量比较重,概念和难点比较集中,而逻辑代数基础的内容很容易为学生所接受,所以将两章的次序对调符合由浅入深的原则。其次,把原来的第四章分成了触发器和时序逻辑电路两章,这样既解决了原来第四章篇幅过大的问题,同时又不影响教材体系的系统性和完整性。再次,考虑到大规模集成电路往往是既包含组合逻辑电路又包含时序逻辑电路的数字系统,所以把大规模集成电路的内容也单独列成了一章。这样,就形成了新版教材的九章体系。

从要求上,正文部分基本上按基本要求编写,略有超出。一部分虽属比较重要但已超出基本要求的内容写在每章的附录中。这些内容既可供那些学时较多、要求较高的院校作为课堂讲授的选讲内容,又可以供学生作为自学的阅读材料。

本书是与童诗白主编的《模拟电子技术基础》(第二版)配套的教材,同时又有相对的独立性。如果将这两本教材配合使用,那么既可以先讲模拟部分、后讲数字部分,也可以先讲数字部分、后讲模拟部分。在先讲数字电路时,只要预先讲过《模拟电子技术基础》(第二版)的第一章即可转入本书的讲授。为了使两学期的学时平衡,可将第八章A/D、D/A转换的内容移到第二学期的模拟部分之后再讲。

第三版的修订工作全部由阎石完成。修订工作得到了童诗白教授的悉心指导。

西安交通大学沈尚贤教授、张庆男副教授、古新生副教授和林雪亮副教授在百忙中仔细地审阅了全部书稿并提出了许多宝贵的意见。多年来,我们的教材工作得到了沈尚贤教授和西安交通大学电子学教研室各位老师的热情关怀和大力支持,在本书出版之际,谨向他们致以最诚挚的

谢意。

许多兄弟院校的师生为本书的修订工作提出过积极的建议和殷切的期望。在收集资料的过程中,得到了上海元件五厂、国营七四九厂、北京半导体器件三厂、上海无线电十四厂、国营四四三五厂有关同志的热情支持,在此一并向他们表示感谢。

新版教材中一定还有不少缺点和不足之处,恳请各界读者给予批评指正。

编 者

1988年5月

## 第四版前言

本书是在《数字电子技术基础》第三版的基础上,按照国家教育委员会高等工业学校电子技术课程教学指导小组于1993年修订的“电子技术基础课程教学基本要求”重新修订而成的。

自《数字电子技术基础》第三版发行以来,数字电子技术的研究和应用又取得了新的进展,其中尤以可编程逻辑器件的广泛应用令世人瞩目。由于可编程逻辑器件等新型器件仍然是制作在硅片上的半导体器件,所以过去用于分析半导体器件工作原理的理论基础对这些新器件也仍然适用。同时,原书中讲授的基本逻辑单元的工作原理以及组合逻辑电路和时序逻辑电路的基本概念、分析方法、设计方法也是使用这些新器件时必须具备的理论基础。

鉴于上述情况,第四版教材在基本保持原书理论体系的基础上,以较大篇幅增补了可编程逻辑器件的内容,单独写成为第八章。将原来的第七章“大规模集成电路”改成“半导体存储器”,仅限于讨论半导体存储器的有关内容。另外,还补充了压控振荡器、快闪存储器等内容,并对自我检测题、思考题和习题作了修改和补充。关于可编程逻辑器件开发工具及其应用的内容准备安排到实验课中结合实际操作讲解,故未在新版教材中作具体介绍。

考虑到许多院校在安排教学计划时都有先上数字电路、后上模拟电路的要求,这次修订时适当增加了半导体二极管、三极管和理想运算放大器基本知识的内容,这样无论是否已经学过模拟电子技术基础,都可以选用这本书作为数字电子技术基础课程的教材。

目录中注有“\*”号的部分是建议作为选讲的内容。在学时较少或要求不高的情况下,建议首先删减这些内容。删去这些内容不会影响理论体系的完整性和内容的连贯性。

此次修订工作全部由阎石教授完成。北京工业大学陆培新教授不辞辛苦地认真审阅了全部书稿,并提出了许多宝贵意见。从本书初版的编写到历次的修订,一直得到童诗白教授的热情支持和悉心指导。作者谨向他们表示衷心的感谢。借此机会也向所有关心、支持和帮助过本书编写、修改、出版、发行工作的同志们致以诚挚的谢意。

修订后的教材中一定还有许多不完善之处,殷切地期望读者给予批评和指正。

编 者

1997年12月

## 第五版前言

---

本书第四版出版以来的 8 年间，数字电子技术的应用一直在继续向着广度和深度扩展。时至今日，“数字化”的浪潮几乎席卷了电子技术应用的一切领域。由于电子产品的更新周期日益缩短，新产品开发速度日益加快，因而对电子设计自动化(EDA)提出了更高的要求，也有力地促进了 EDA 技术的发展和普及。在数字集成电路方面，尽管电路的集成度仍然如摩尔定律(Moore's Law)所预言的那样，以每 1~2 年翻一番的速度增长，使电路的复杂程度越来越高、规模越来越大，但是它仍然没有走出“硅片”的范畴。因此，本门课程所讲的基本知识、基本理论和基本方法也没有发生根本性的改变。而在基本技能方面，则对使用 EDA 工具的能力提出了更高的要求。

2004 年秋天在“教育部电子信息科学与电气信息类基础课程教学指导分委员会”的主持下，重新修订了“数字电子技术基础课程教学基本要求”。基本要求再次强调了本门课程的性质是“电子技术方面入门性质的技术基础课”，其任务在于“使学生获得数字电子技术方面的基本知识、基本理论和基本技能，为深入学习数字电子技术及其在专业中的应用打下基础”。

根据数字电子技术本身的发展状况和修订后的基本要求，在基本保持本书第四版原有内容、体系和风格的基础上，主要做了以下几方面的修改和补充：

一、将原来第一章“逻辑代数基础”中数制和编码的内容分离出来，单独编为第一章“数制和码制”，并补充了有关二进制补码运算原理的内容。

二、重新改写了第三章“门电路”和第五章“触发器”。在“门电路”一章里，将 CMOS 电路放在了更主要的位置。在“触发器”一章中，改为按触发方式将触发器分类讲授，更加强调外部特性而淡化内部的具体电路结构。

三、根据修订的基本要求，增加了第九章“硬件描述语言”，初步介绍了有关硬件描述语言的基本知识。同时，还在有些章节中增加了使用 Multisim 7 分析和仿真数字逻辑电路的简单内容。这里只是希望给读者一些初步的概念，因为真正掌握这两部分内容还必须通过后续课程的学习和实践应用才能达到。

四、在多数小结的末尾增加了复习思考题。删去了第四版中每章后面的自我检测题以及一些非基本的内容(如动态移位寄存器、非精密的压控振荡器、串行输入的 D/A 转换器、串行输出的 A/D 转换器等)。

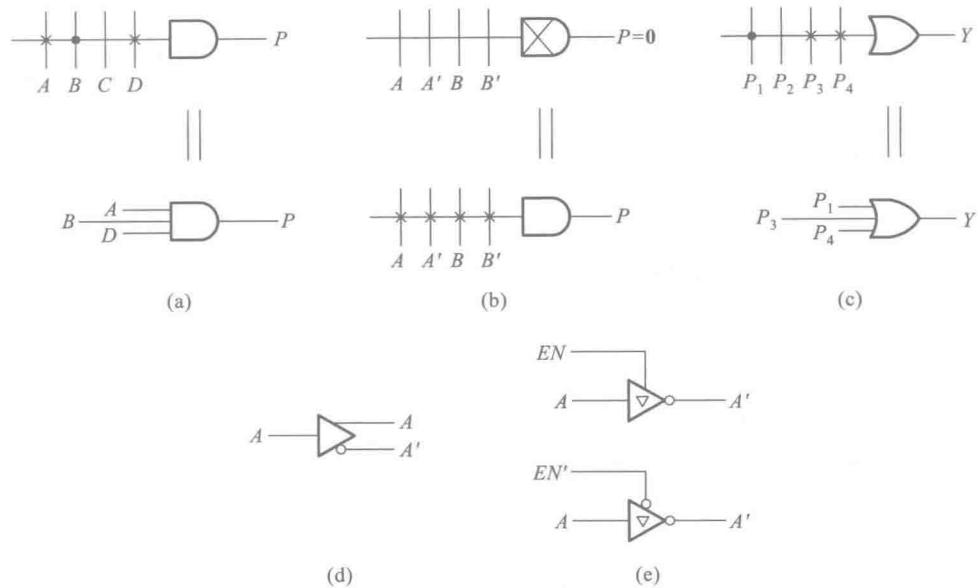

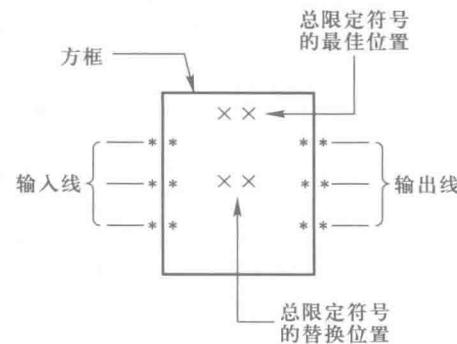

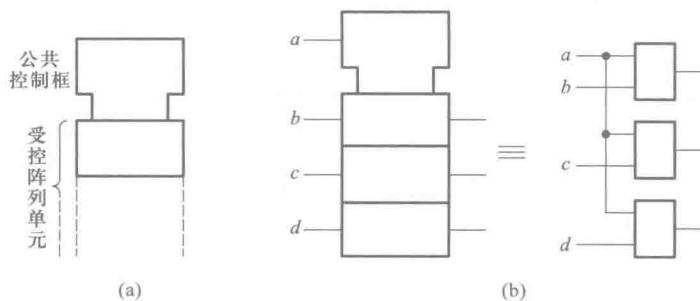

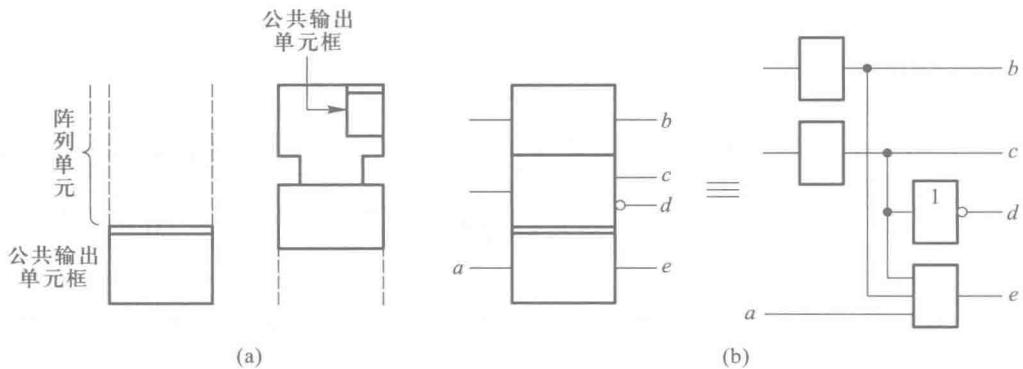

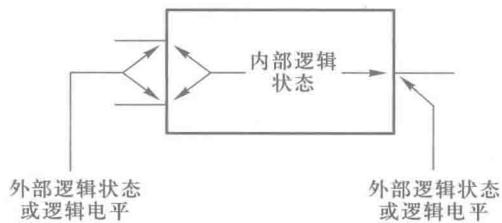

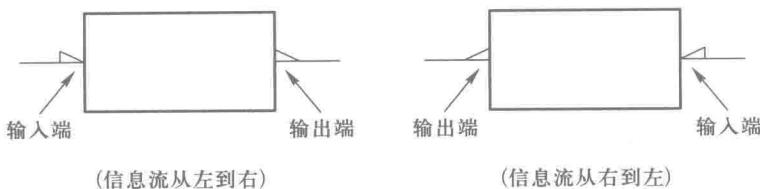

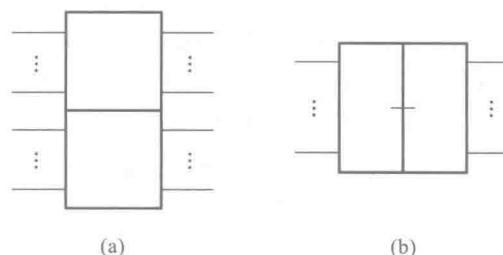

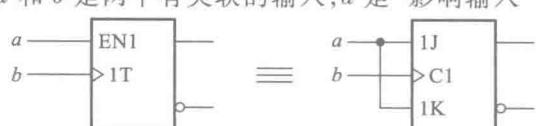

五、采用了国际上流行的图形逻辑符号。其中基本运算和复合运算的符号采用了特定外形的图形符号。这种特定外形的图形符号已经补充到 1991 年修订的 IEEE/ANSI(The Institute of Electrical and Electronics Engineers/American National Standards Institute, 电气与电子工程师协会/美国国家标准化组织)标准中，而且与 IEC(The International Electrotechnical Commission, 国际电

工协会)的标准是兼容的。我国现行的图形逻辑符号国家标准(GB 4728.12—85)是参照修订前的 IEEE 和 IEC 标准制定的,尚未见做相应的修改。为便于教学,中、大规模集成电路的图形符号仍旧采用国外教材、技术资料和 EDA 软件中普遍使用的习惯画法,即示意性框图画法。

目录中注有“\*”号的部分是建议作为选讲的内容。略去这些内容不影响理论体系的完整性和内容的连贯性。

在本次的修订工作中,王红执笔编写了第九章和第六章的 6.6 节、第十章的 10.6 节,其余章节的修改和编写工作全部由阎石完成。北京工业大学陆培新教授不辞辛劳地认真审阅了全部书稿,并提出了不少宝贵意见。许多教师和同学也热情地为本次修订工作提出了很好的意见和建议。作者谨向他们致以诚挚的谢意。

从本书初版的编写到历次的修订都得到了我的老师童诗白教授的悉心指导。如今童诗白教授已经离开了我们,作者以深切的怀念和感激之情铭记着老师的教诲,愿继续努力做好教材的编写和修订工作,以谢师恩。

修订后的第五版教材一定还会有许多不尽如人意之处,恳请读者批评指正。

阎 石

2005 年岁末

# 本书中的文字符号及其说明

## 一、电压符号

$v_i$  输入电压(相对于电路公共参考点的电压)

$V_{IH}$  输入高电平

$V_{IL}$  输入低电平

$v_o$  输出电压(相对于电路公共参考点的电压)

$V_{OH}$  输出高电平

$V_{OL}$  输出低电平

$V_T$  温度电压当量

$V_{CC}$  电源电压(一般用于双极型半导体器件)

$V_{CE(sat)}$  三极管集电极与发射极间的饱和导通压降(一般用于双极型三极管)

$V_{DD}$  电源电压(一般用于 MOS 器件)

$v_{BE}$  三极管基极相对于发射极的电压

$v_{CE}$  三极管集电极相对于发射极的电压

$v_{DS}$  MOS 管漏极相对于源极的电压

$v_{GS}$  MOS 管栅极相对于源极的电压

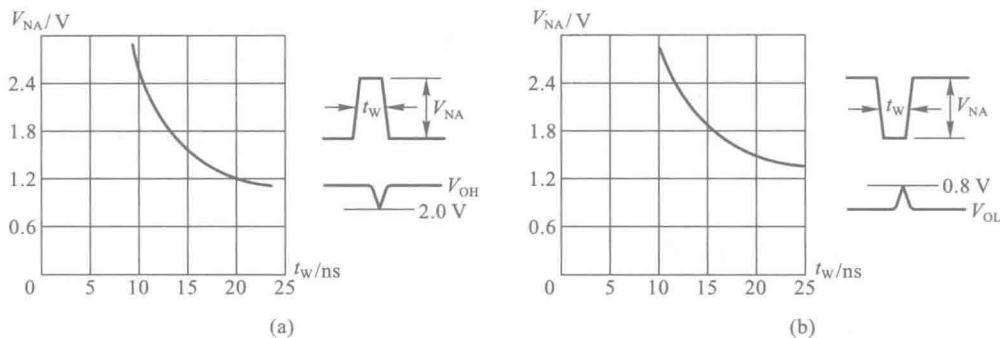

$V_{NA}$  脉冲噪声电压幅值

$V_{NH}$  输入高电平噪声容限

$V_{NL}$  输入低电平噪声容限

$V_{TH}$  门电路的阈值电压

$V_{T+}$  施密特触发特性的正向阈值电压

$V_{T-}$  施密特触发特性的负向阈值电压

$V_{GS(n)N}$  N 沟道 MOS 管的开启电压

$V_{GS(p)P}$  P 沟道 MOS 管的开启电压

$V_{REF}$  参考电压(或基准电压)

## 二、电流符号

$i_b(I_B)$  基极电流瞬时值(直流量)

$I_{BS}$  饱和基极电流

$i_c(I_C)$  集电极电流瞬时值(直流量)

$i_d(I_D)$  漏极电流瞬时值(直流量)

$i_i$  输入电流

## II 本书中的文字符号及其说明

|                  |                           |

|------------------|---------------------------|

| $I_{\text{IH}}$  | 高电平输入电流                   |

| $I_{\text{IL}}$  | 低电平输入电流                   |

| $i_L (I_L)$      | 负载电流瞬时值(直流量)              |

| $i_o$            | 输出电流                      |

| $I_{\text{OH}}$  | 高电平输出电流                   |

| $I_{\text{OL}}$  | 低电平输出电流                   |

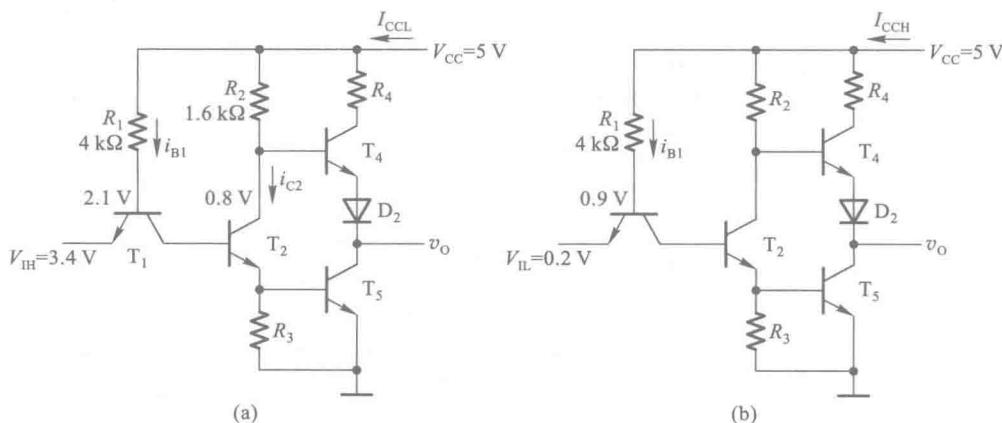

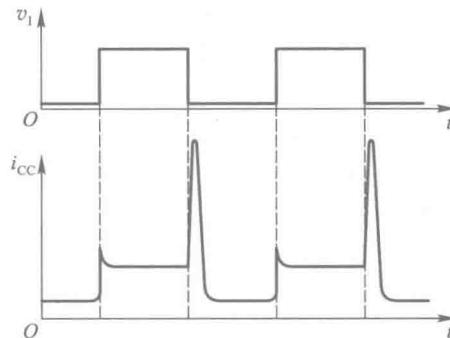

| $I_{\text{CC}}$  | 电源( $V_{\text{cc}}$ )平均电流 |

| $I_{\text{ccb}}$ | 输出为高电平时的电源电流              |

| $I_{\text{ccl}}$ | 输出为低电平时的电源电流              |

| $I_{\text{DD}}$  | 电源( $V_{\text{dd}}$ )平均电流 |

### 三、功率符号

|                  |                    |

|------------------|--------------------|

| $P_c$            | CMOS 电路中负载电容充、放电功耗 |

| $P_d$            | CMOS 电路的动态功耗       |

| $P_s$            | CMOS 电路的静态功耗       |

| $P_t$            | CMOS 电路的瞬时导通功耗     |

| $P_{\text{tot}}$ | CMOS 电路的总功耗        |

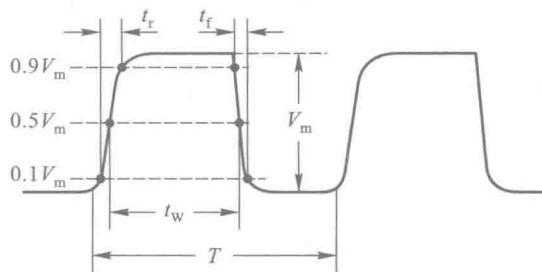

### 四、脉冲参数符号

|           |            |

|-----------|------------|

| $f$       | 周期性脉冲的重复频率 |

| $q$       | 占空比        |

| $t_f$     | 下降时间       |

| $t_h$     | 保持时间       |

| $t_r$     | 上升时间       |

| $t_{re}$  | 恢复时间       |

| $t_{set}$ | 建立时间       |

| $t_w$     | 脉冲宽度       |

| $V_m$     | 脉冲幅度       |

### 五、电阻、电容符号

|                      |                                |

|----------------------|--------------------------------|

| $C_{GD}$             | MOS 管栅极与漏极间的电容                 |

| $C_{GS}$             | MOS 管栅极与源极间的电容                 |

| $C_h$                | 保持电容                           |

| $C_i$                | 输入电容                           |

| $C_L$                | 负载电容                           |

| $R_{GE(\text{sat})}$ | 三极管集电极与发射极间的饱和导通电阻(一般用于双极型三极管) |

| $R_i$                | 输入电阻                           |

| $R_L$                | 负载电阻                           |

| $R_o$                | 输出电阻                           |

| $R_{OFF}$            | 器件截止时的内阻                       |

| $R_{ON}$             | 器件导通时的内阻                       |

$R_U$  上拉电阻

## 六、器件及参数符号

A 放大器

$A_v$  放大器的电压放大倍数

$C_{pd}$  CMOS 电路的功耗电容

D 二极管

FF 触发器

$pd$  延迟-功耗积

PLD 可编程逻辑器件

G 门

S 开关

T 三极管

$T_N$  N 沟道 MOS 管

$T_P$  P 沟道 MOS 管

TG 传输门

$t_{pd}$  平均传输延迟时间

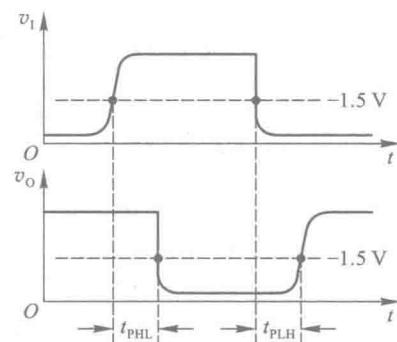

$t_{PHL}$  输出由高电平变为低电平时的传输延迟时间

$t_{PLH}$  输出由低电平变为高电平时的传输延迟时间

## 七、其他符号

B 二进制

$CLK$  时钟

$CS$  片选

D 十进制

$EN$  允许(使能)

GND 接地端

H 十六进制

$OE$  输出允许(使能)

$R/W'$  读/写

$\Sigma$  求和

# 目录

---

|                          |           |

|--------------------------|-----------|

| 绪论 .....                 | 1         |

| <b>第一章 数制和码制 .....</b>   | <b>4</b>  |

| 1.1 概述 .....             | 4         |

| 1.2 几种常用的数制 .....        | 4         |

| 1.3 不同数制间的转换 .....       | 6         |

| 1.4 二进制算术运算 .....        | 9         |

| 1.4.1 二进制算术运算的特点 .....   | 9         |

| 1.4.2 反码、补码和补码运算 .....   | 10        |

| 1.5 几种常用的编码 .....        | 13        |

| 本章小结 .....               | 18        |

| 习题 .....                 | 18        |

| <b>第二章 逻辑代数基础 .....</b>  | <b>20</b> |

| 2.1 概述 .....             | 20        |

| 2.2 逻辑代数中的三种基本运算 .....   | 20        |

| 2.3 逻辑代数的基本公式和常用公式 ..... | 24        |

| 2.3.1 基本公式 .....         | 24        |

| 2.3.2 若干常用公式 .....       | 25        |

| 2.4 逻辑代数的基本定理 .....      | 27        |

| 2.4.1 代入定理 .....         | 27        |

| 2.4.2 反演定理 .....         | 27        |

| 2.4.3 对偶定理 .....         | 28        |

| 2.5 逻辑函数及其描述方法 .....     | 29        |

| 2.5.1 逻辑函数 .....         | 29        |

| 2.5.2 逻辑函数的描述方法 .....    | 29        |

| 2.5.3 逻辑函数的两种标准形式 .....  | 34        |

| 2.6 逻辑函数的化简方法 .....      | 37        |

| 2.6.1 公式化简法 .....        | 37        |

| 2.6.2 卡诺图化简法 .....       | 40        |

|                                  |    |

|----------------------------------|----|

| * 2.6.3 奎恩-麦克拉斯基化简法(Q-M 法) ..... | 44 |

| 2.7 具有关项的逻辑函数及其化简 .....          | 47 |

| 2.7.1 约束项、任意项和逻辑函数式中的无关项 .....   | 47 |

| 2.7.2 无关项在化简逻辑函数中的应用 .....       | 49 |

| 2.8 多输出逻辑函数的化简 .....             | 50 |

| 2.9 逻辑函数形式的变换 .....              | 52 |

| 本章小结 .....                       | 54 |

| 习题 .....                         | 55 |

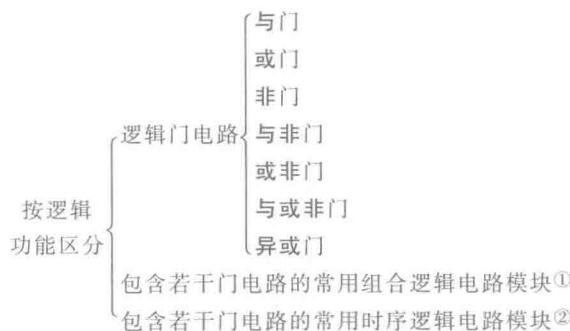

### 第三章 门电路 ..... 62

|                                  |     |

|----------------------------------|-----|

| 3.1 概述 .....                     | 62  |

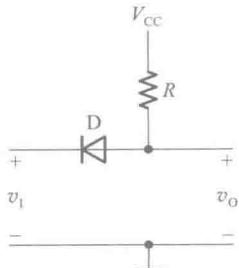

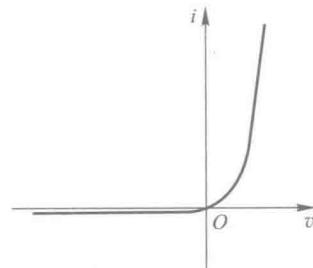

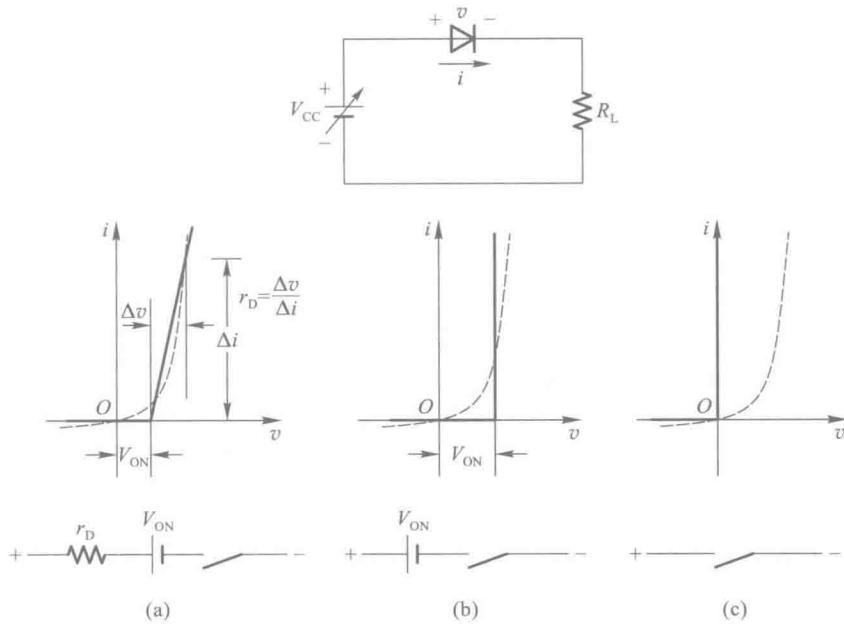

| 3.2 半导体二极管门电路 .....              | 64  |

| 3.2.1 半导体二极管的开关特性 .....          | 64  |

| 3.2.2 二极管与门 .....                | 66  |

| 3.2.3 二极管或门 .....                | 67  |

| 3.3 CMOS 门电路 .....               | 68  |

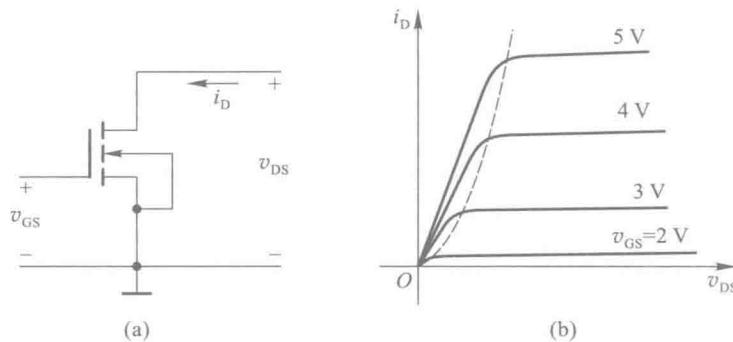

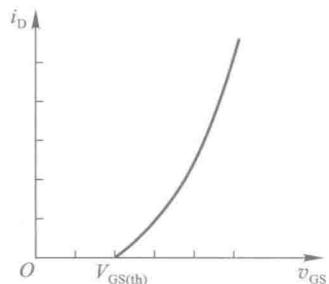

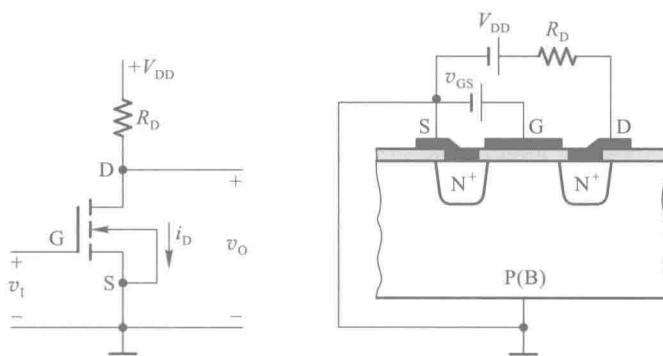

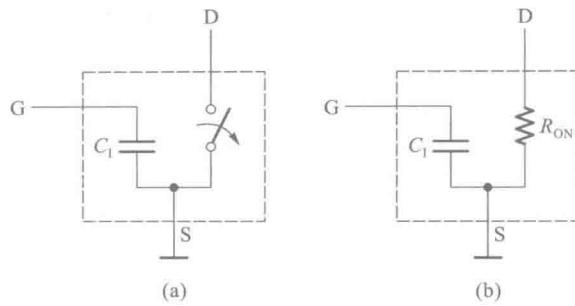

| 3.3.1 MOS 管的开关特性 .....           | 68  |

| 3.3.2 CMOS 反相器的电路结构和工作原理 .....   | 73  |

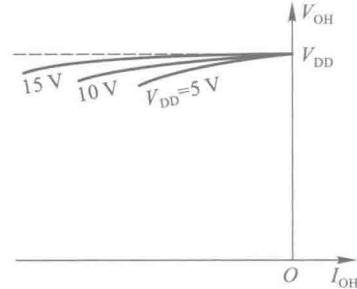

| 3.3.3 CMOS 反相器的静态输入特性和输出特性 ..... | 77  |

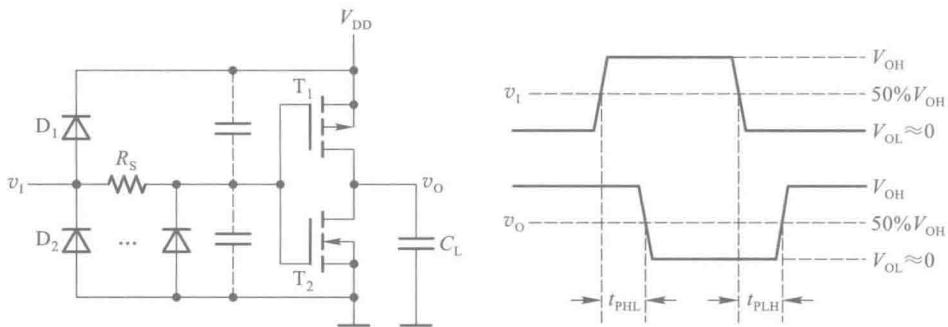

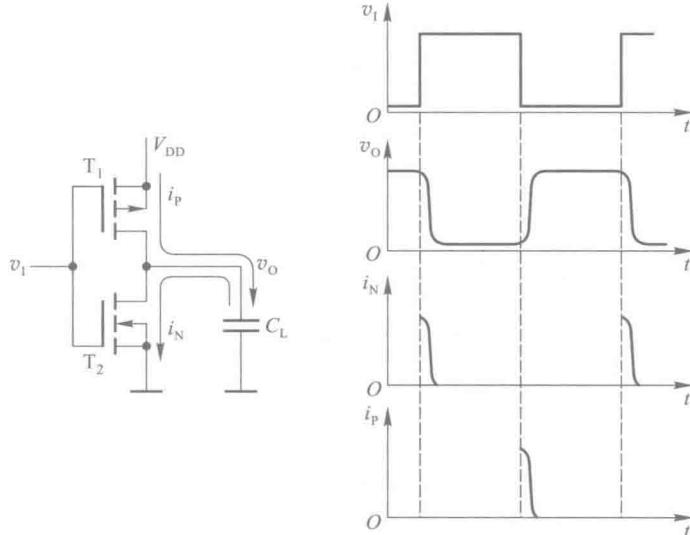

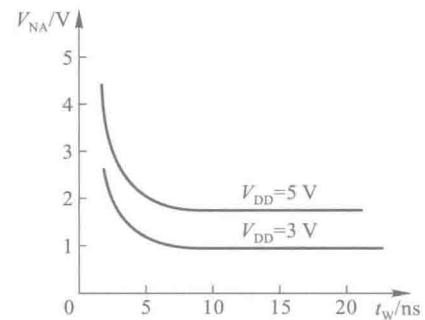

| 3.3.4 CMOS 反相器的动态特性 .....        | 80  |

| 3.3.5 其他类型的 CMOS 门电路 .....       | 85  |

| 3.3.6 CMOS 集成电路的正确使用 .....       | 92  |

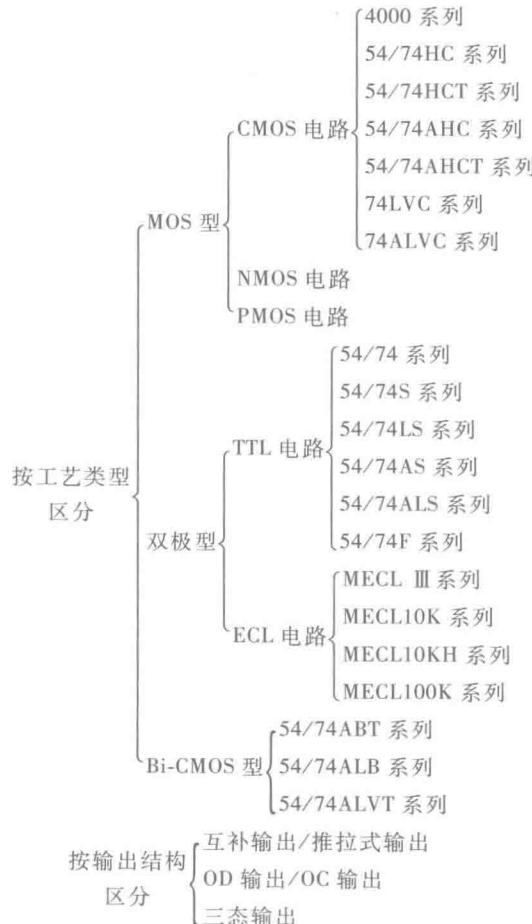

| 3.3.7 CMOS 数字集成电路的各种系列 .....     | 96  |

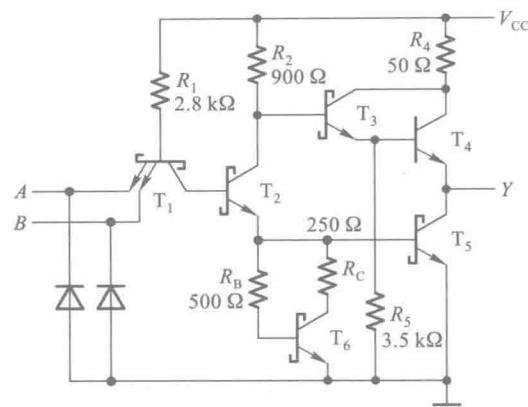

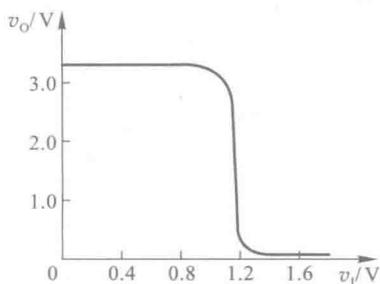

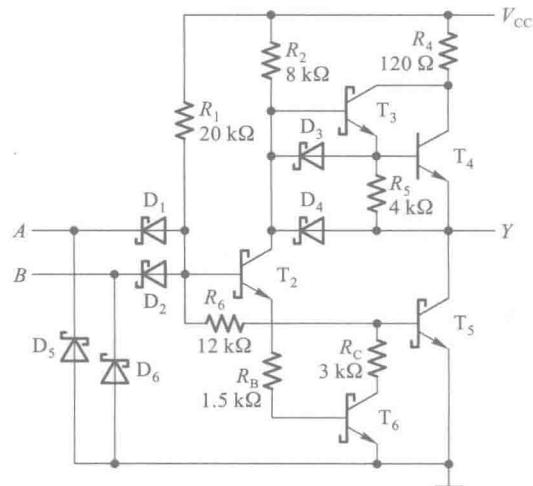

| 3.4 TTL 门电路 .....                | 99  |

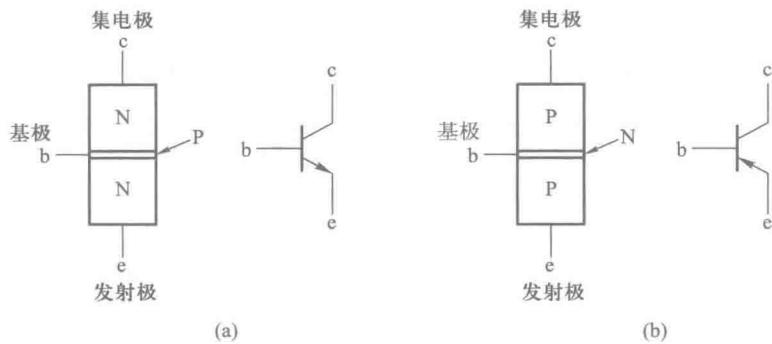

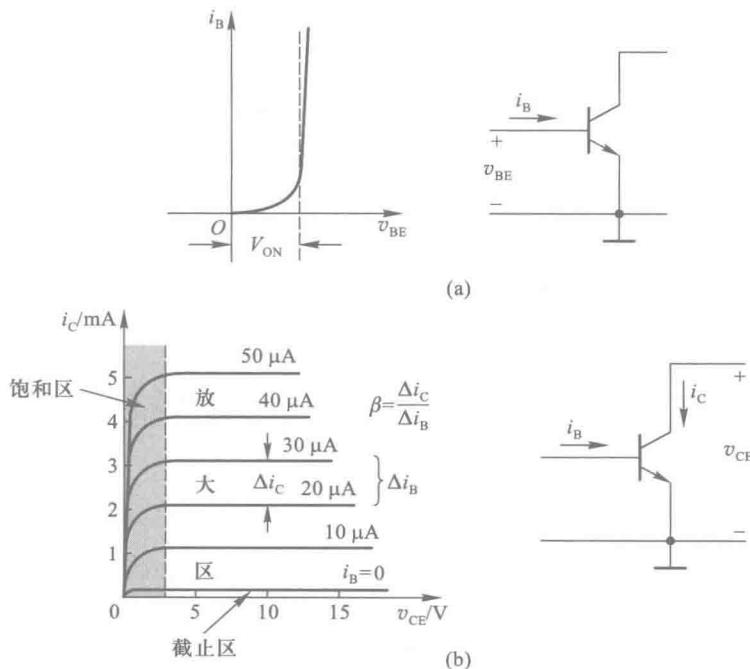

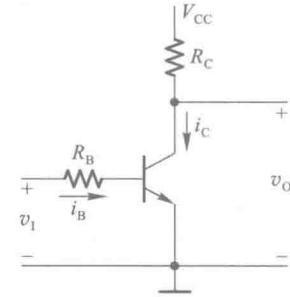

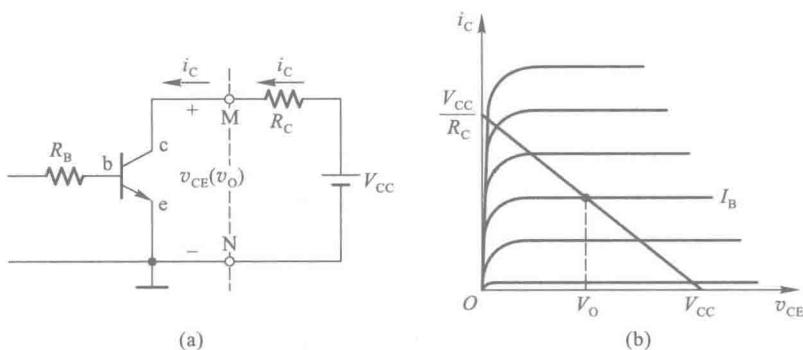

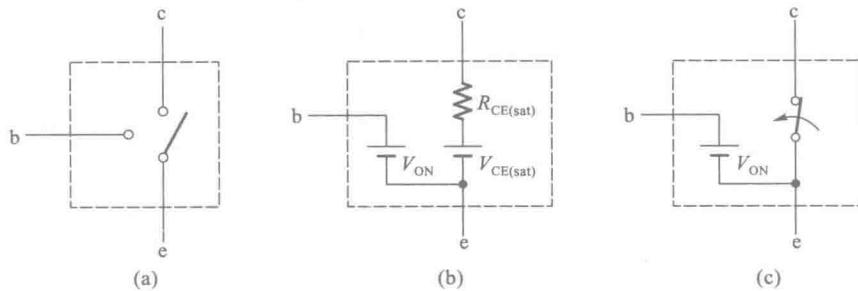

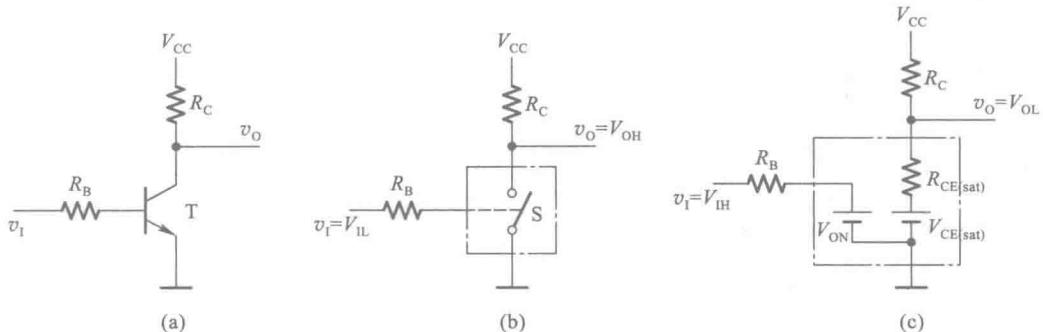

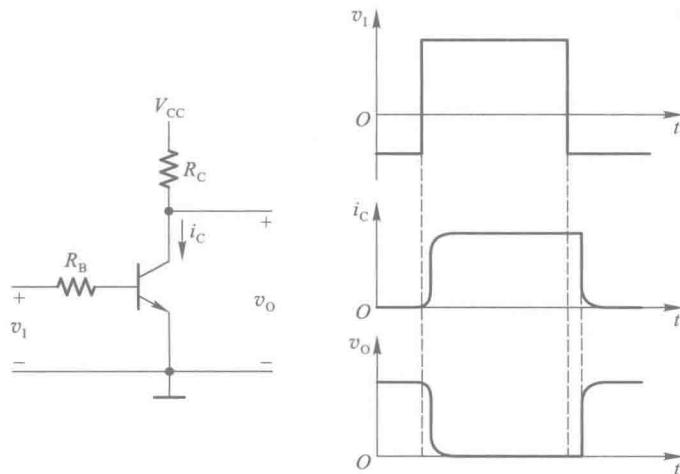

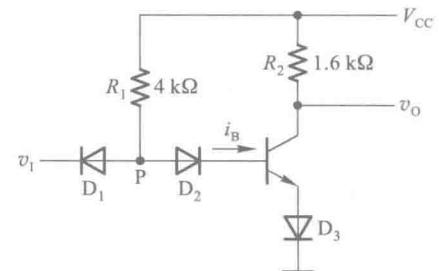

| 3.4.1 双极型三极管的开关特性 .....          | 99  |

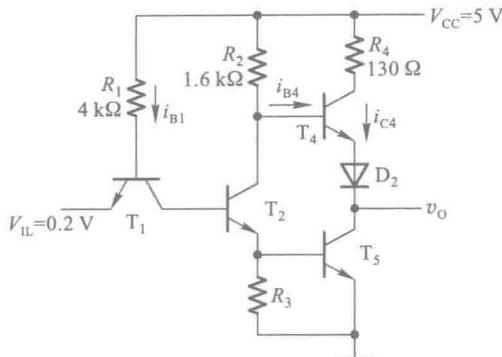

| 3.4.2 TTL 反相器的电路结构和工作原理 .....    | 105 |

| 3.4.3 TTL 反相器的静态输入特性和输出特性 .....  | 107 |

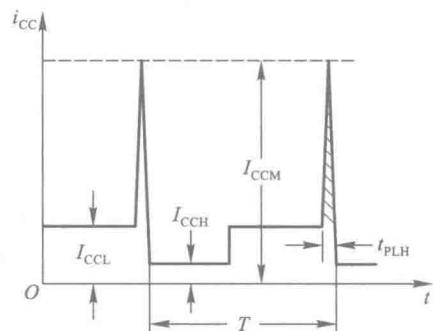

| 3.4.4 TTL 反相器的动态特性 .....         | 111 |

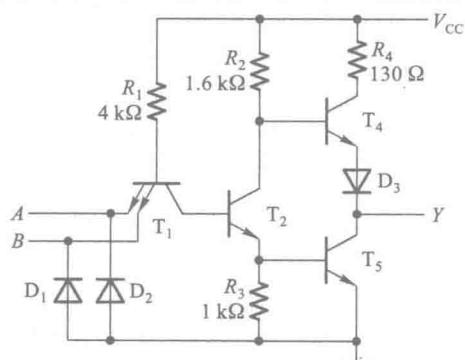

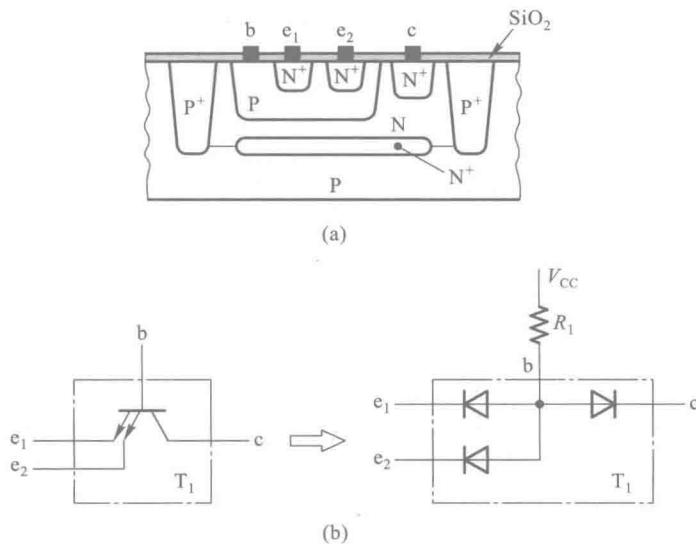

| 3.4.5 其他类型的 TTL 门电路 .....        | 115 |

| 3.4.6 TTL 数字集成电路的各种系列 .....      | 122 |

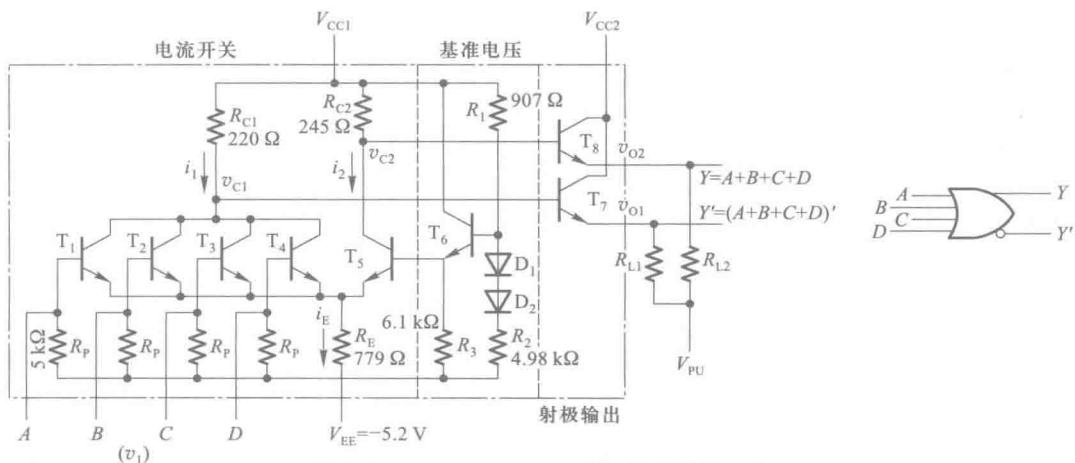

| * 3.5 ECL 集成电路 .....             | 126 |

| 3.5.1 ECL 电路的基本结构和工作原理 .....     | 126 |

| 3.5.2 ECL 集成电路的各种系列 .....        | 128 |

| 3.6 Bi-CMOS 电路 .....             | 129 |

| 3.6.1 Bi-CMOS 电路的基本结构和工作原理 ..... | 129 |

| 3.6.2 Bi-CMOS 集成电路的各种系列 .....    | 130 |

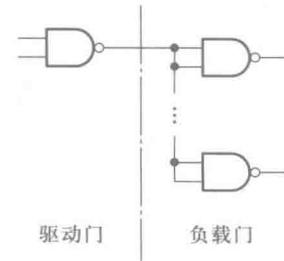

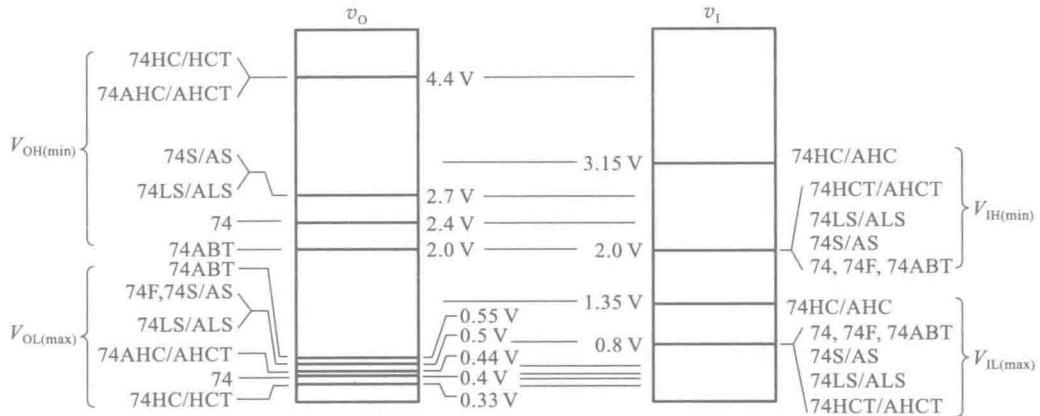

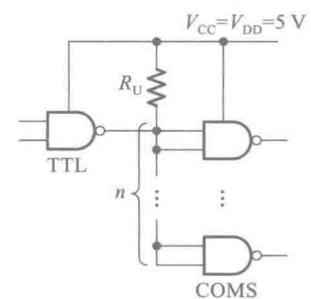

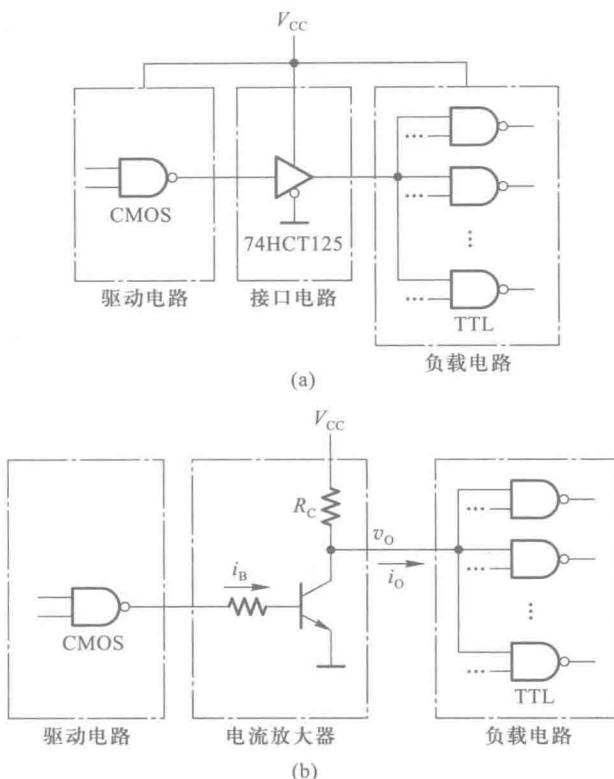

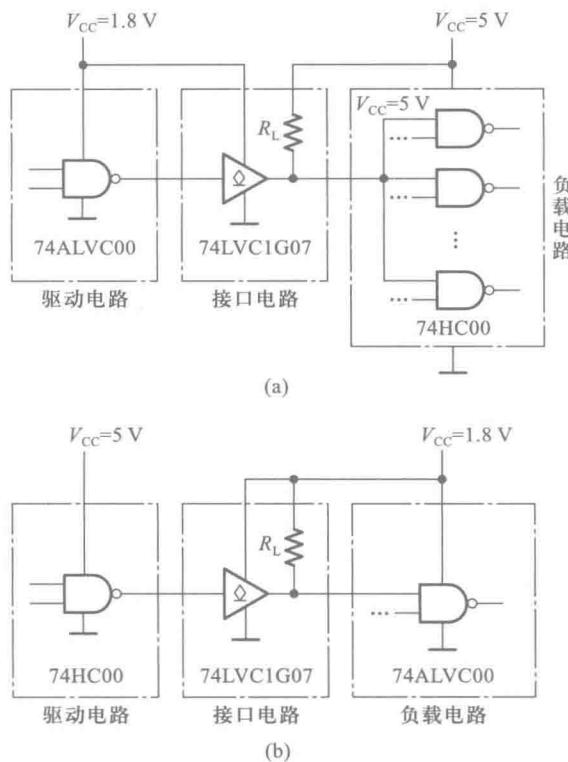

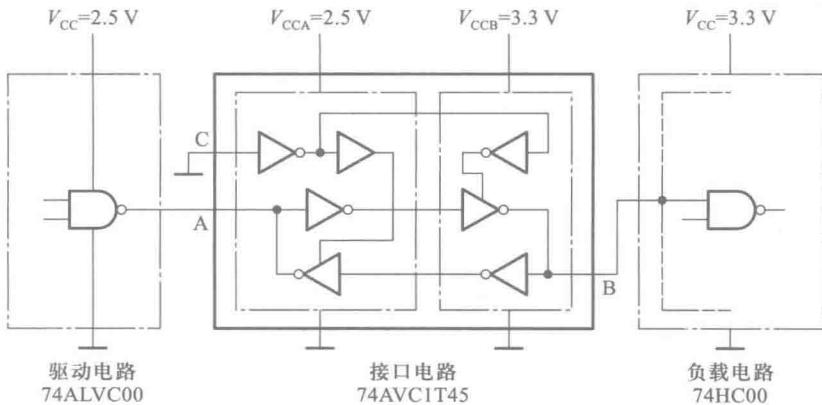

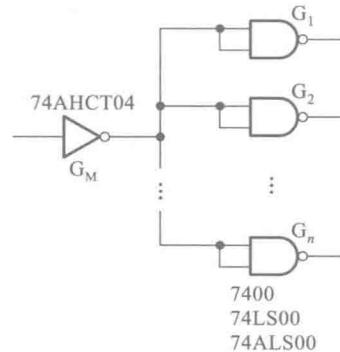

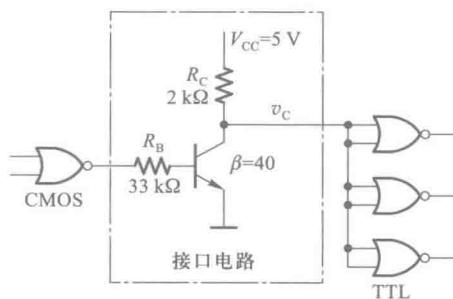

| 3.7 不同类型数字集成电路间的接口 .....         | 132 |

| 3.7.1 CMOS 电路和 TTL 电路的接口 .....   | 132 |

|                              |            |

|------------------------------|------------|

| 3.7.2 不同逻辑电平电路间的接口 ······    | 134        |

| 本章小结 ······                  | 136        |

| 习题 ······                    | 139        |

| <br>                         |            |

| <b>第四章 组合逻辑电路 ······</b>     | <b>146</b> |

| 4.1 概述 ······                | 146        |

| 4.2 组合逻辑电路的分析方法 ······       | 147        |

| 4.3 组合逻辑电路的基本设计方法 ······     | 149        |

| 4.4 若干常用的组合逻辑电路模块 ······     | 152        |

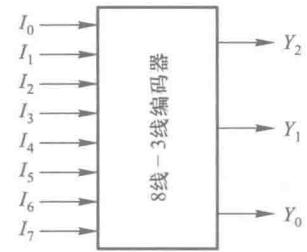

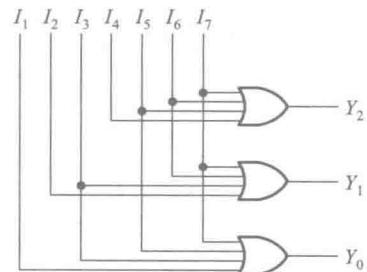

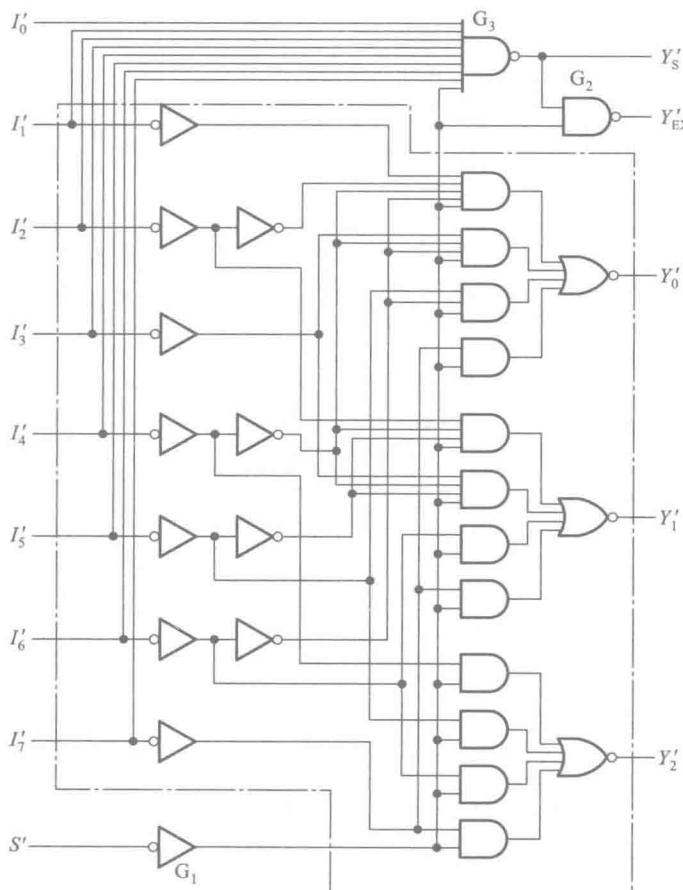

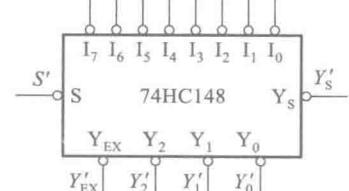

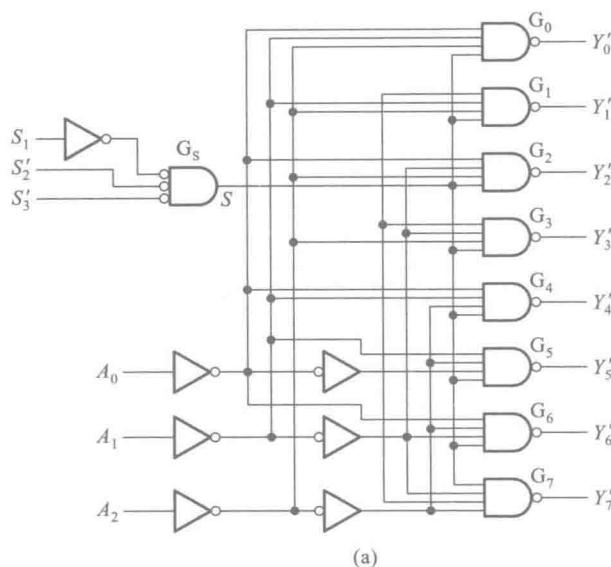

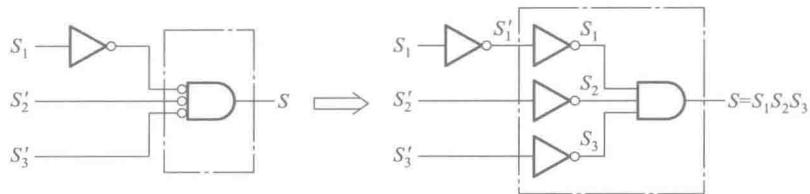

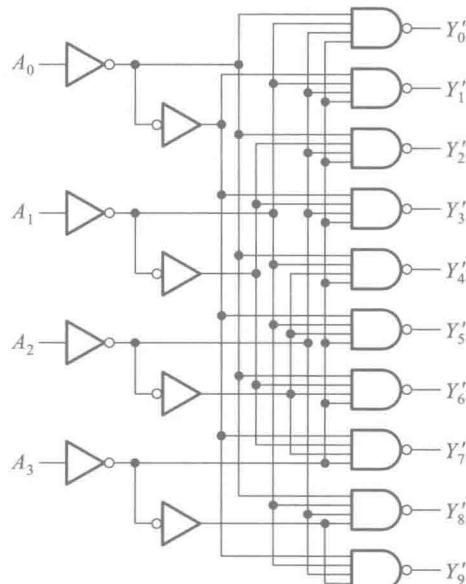

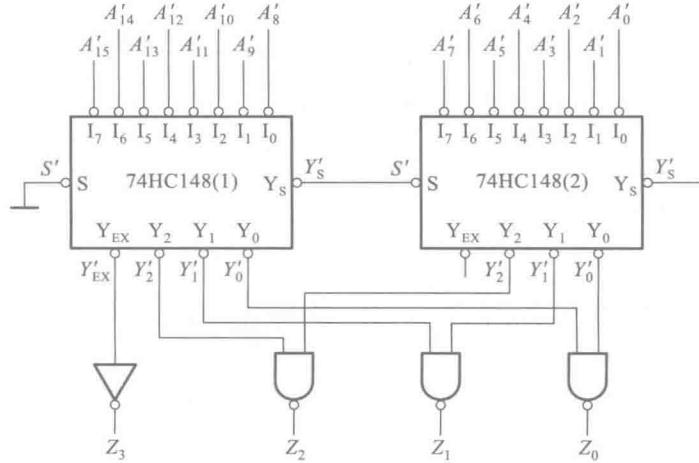

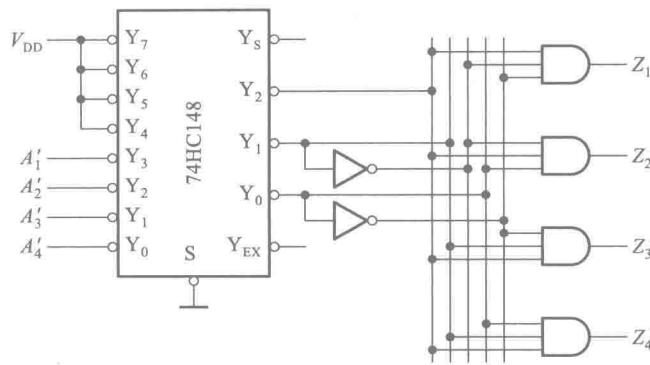

| 4.4.1 编码器 ······             | 153        |

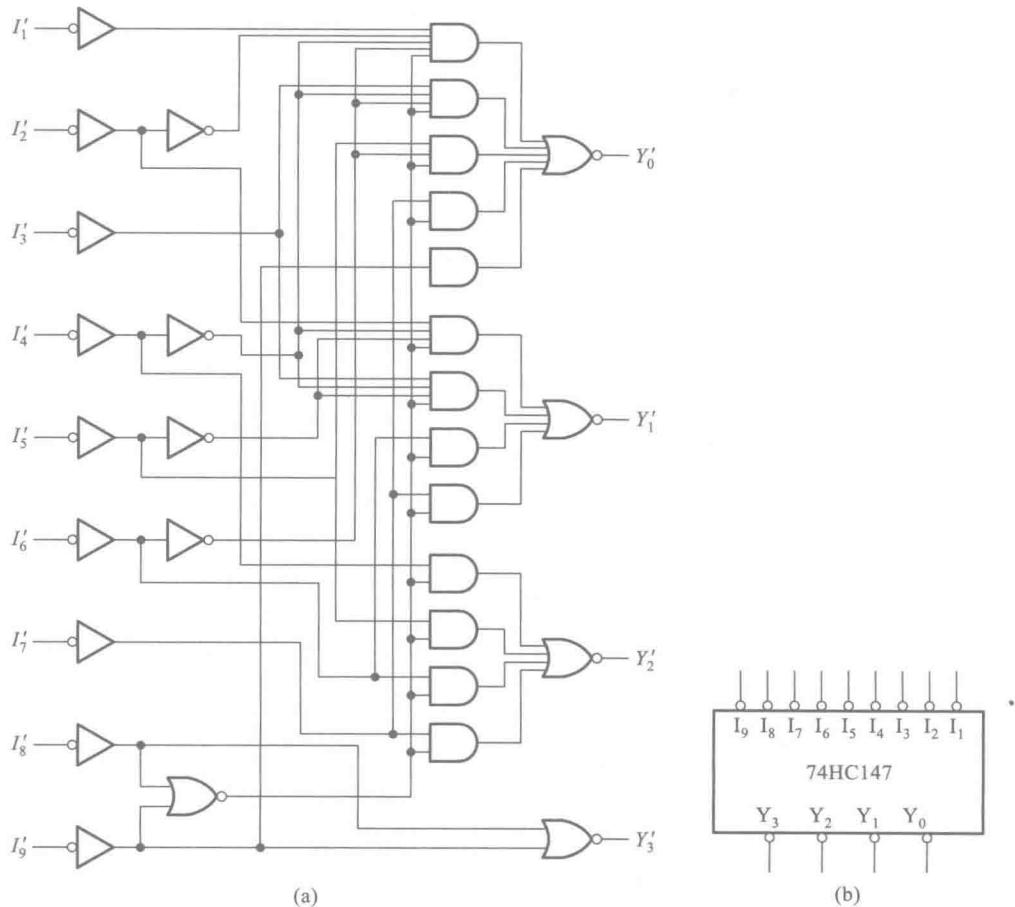

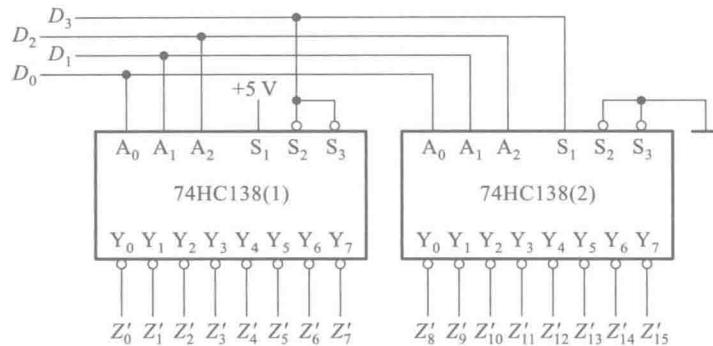

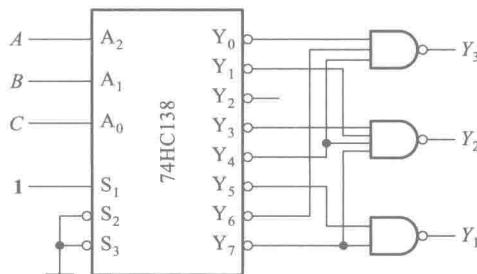

| 4.4.2 译码器 ······             | 157        |

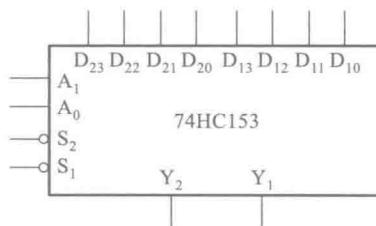

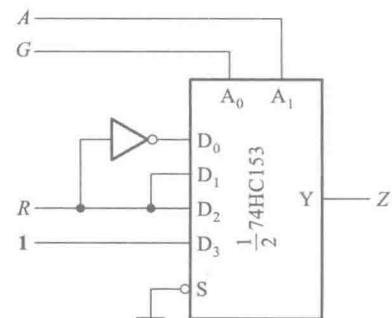

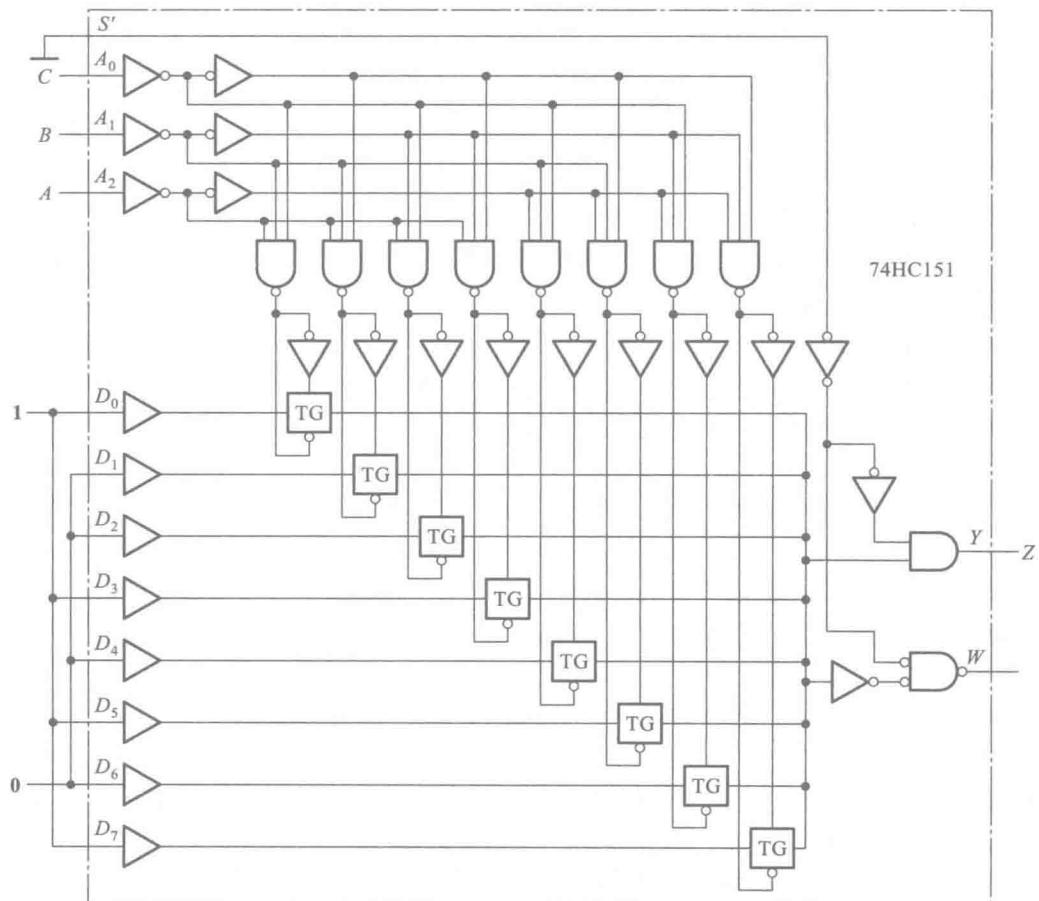

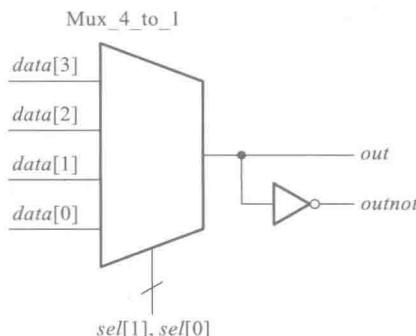

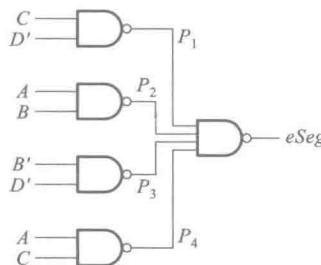

| 4.4.3 数据选择器 ······           | 170        |

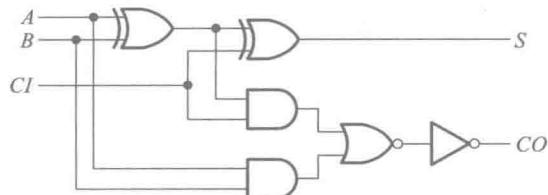

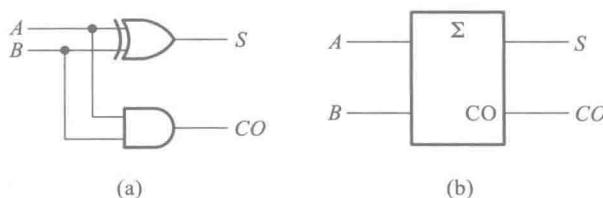

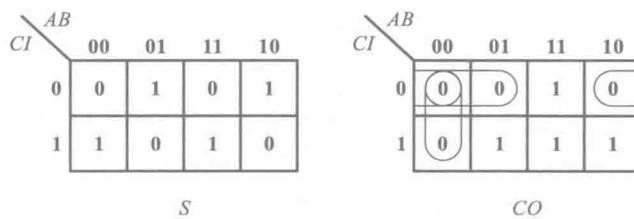

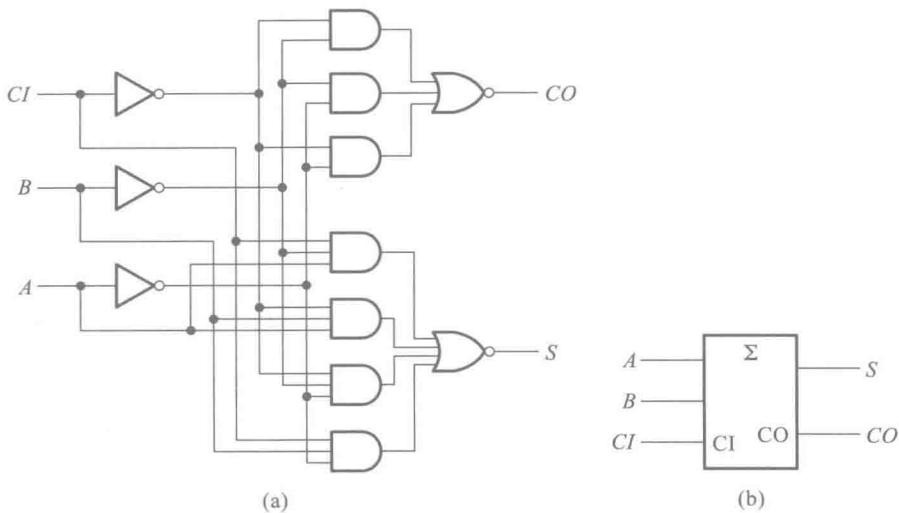

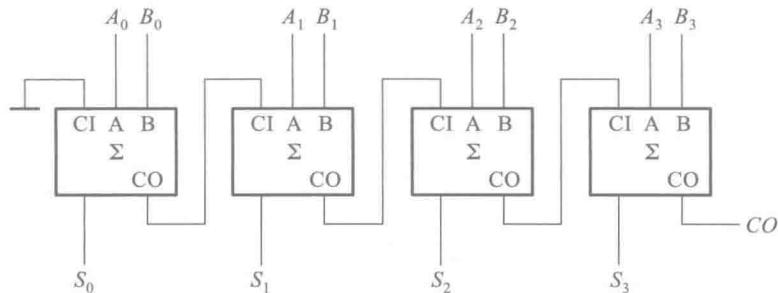

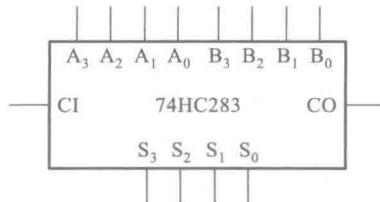

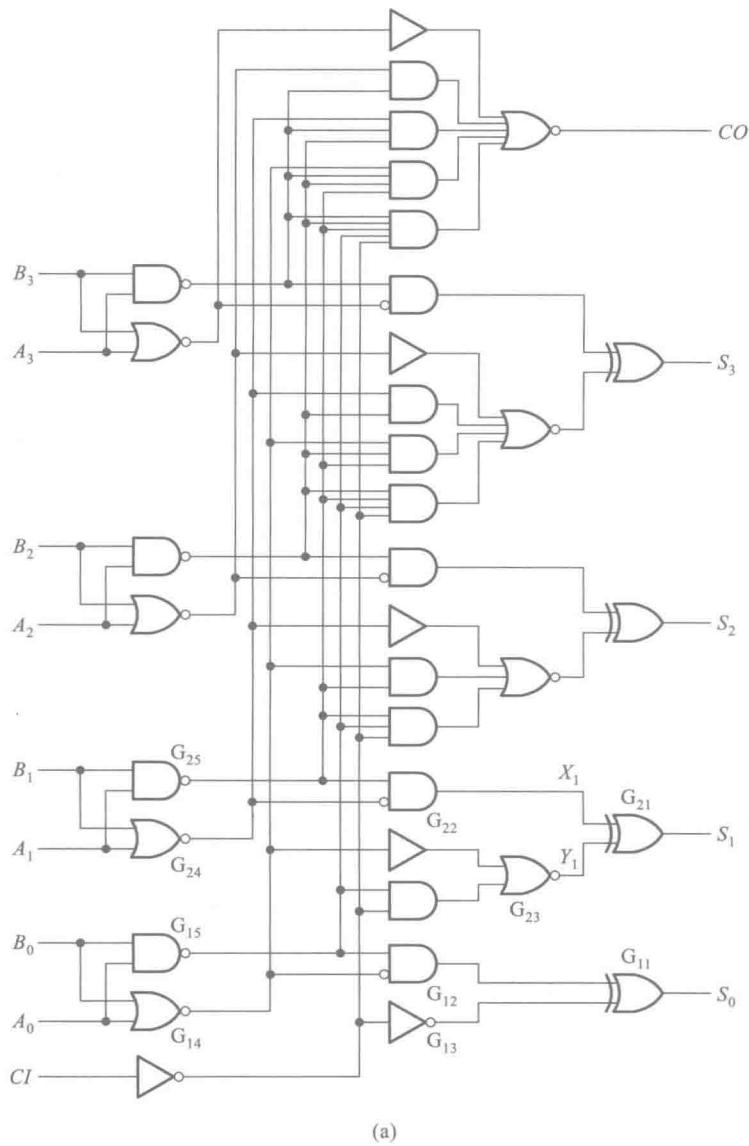

| 4.4.4 加法器 ······             | 172        |

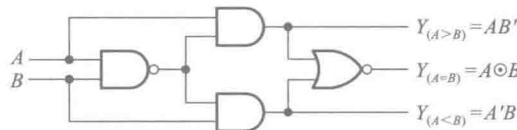

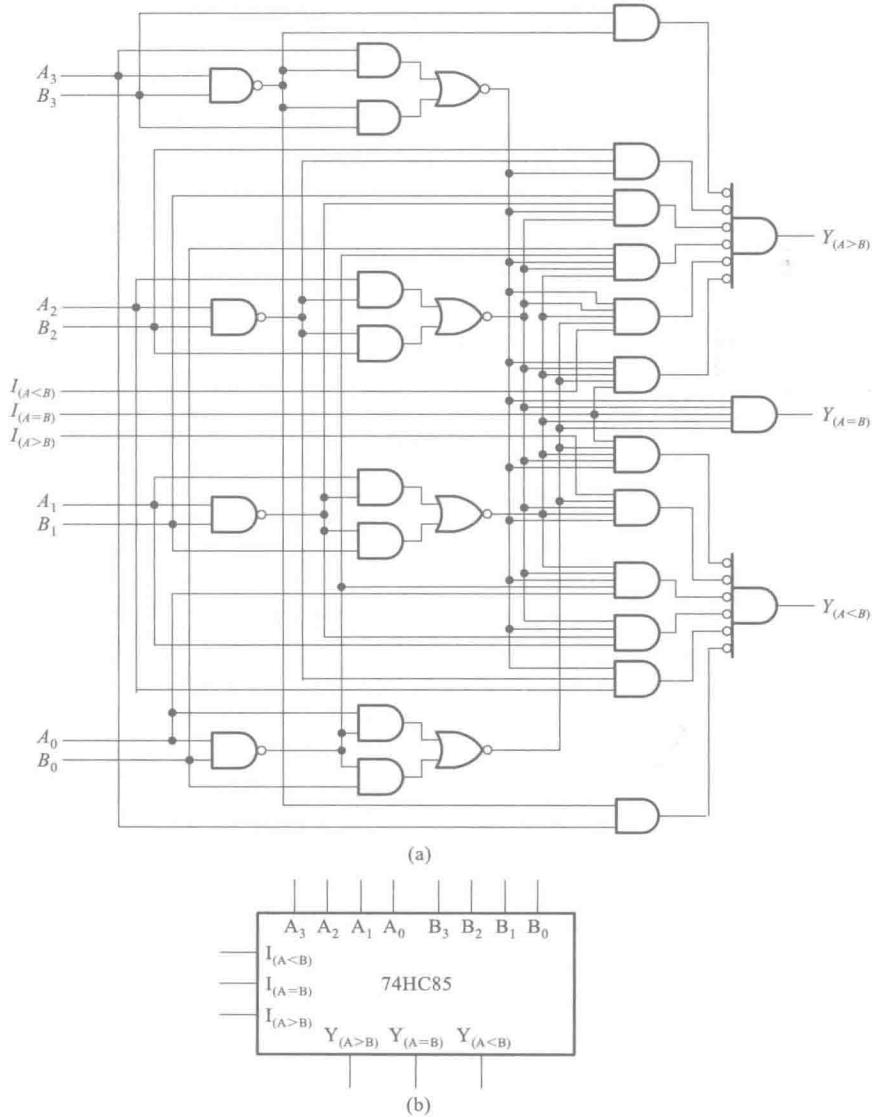

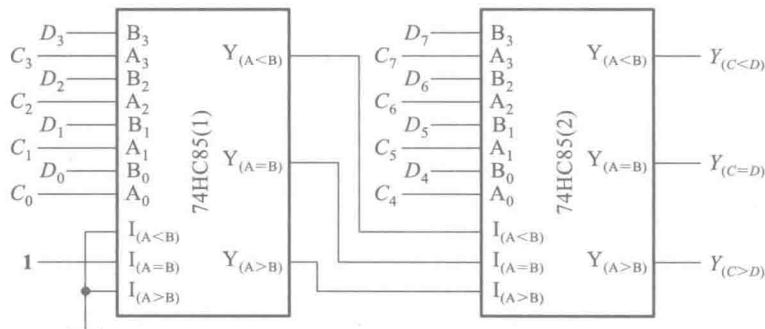

| 4.4.5 数值比较器 ······           | 177        |

| 4.5 层次化和模块化的设计方法 ······      | 179        |

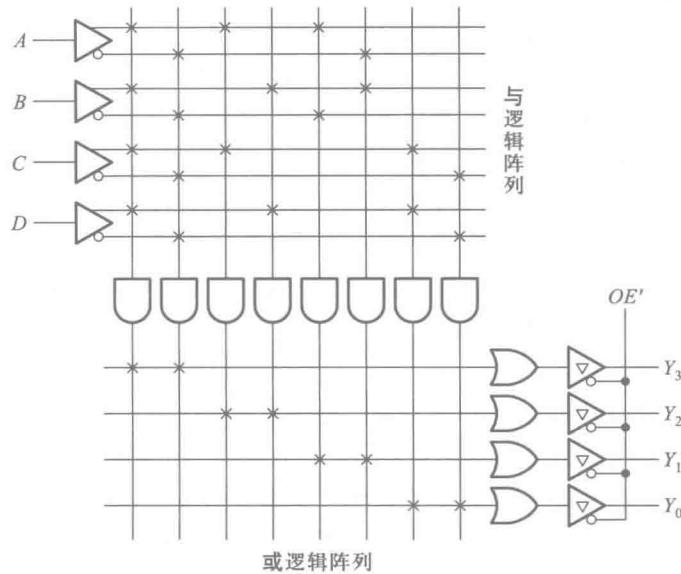

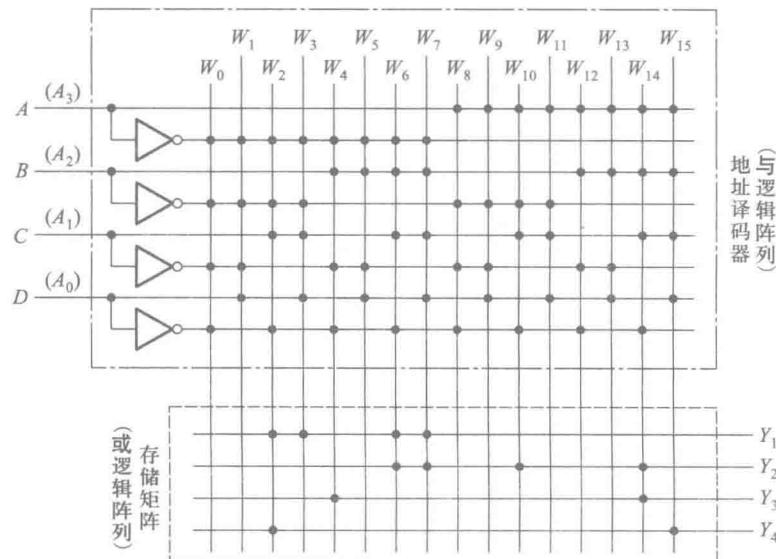

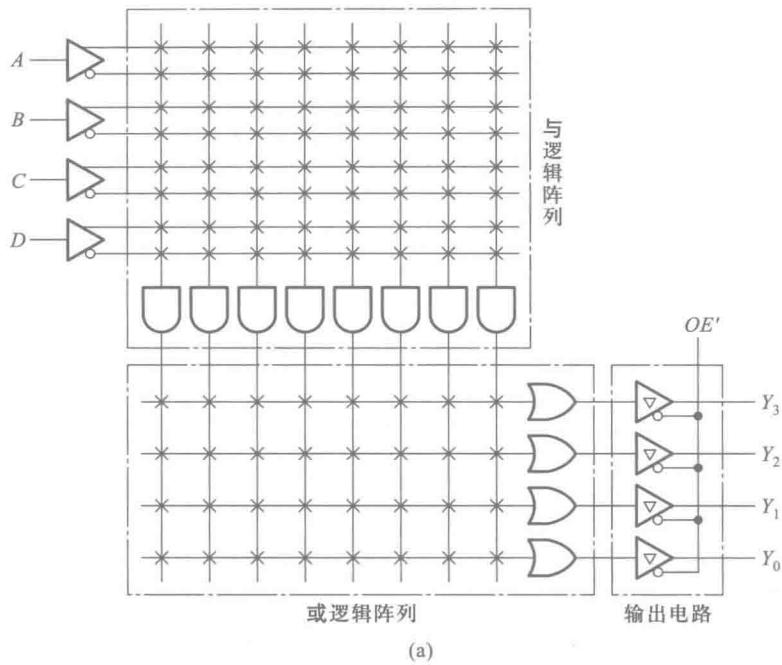

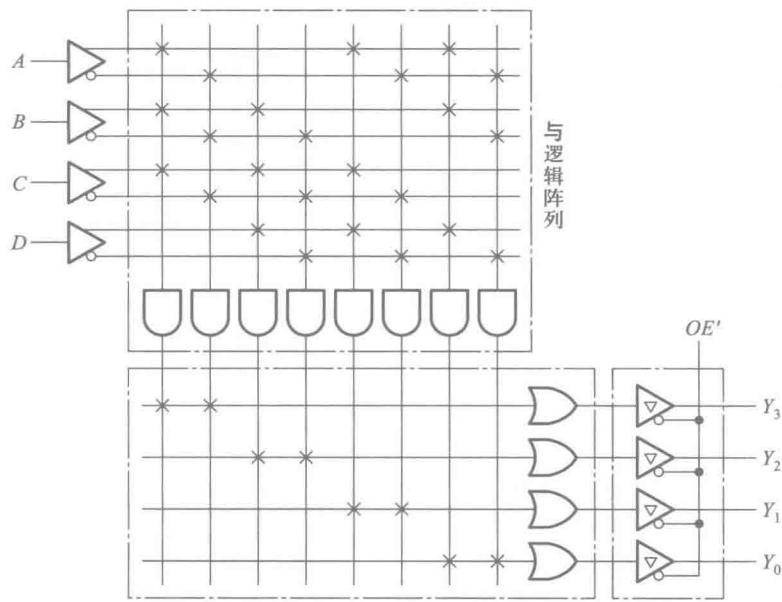

| 4.6 可编程逻辑器件 ······           | 184        |

| 4.7 硬件描述语言 ······            | 186        |

| 4.8 用可编程通用模块设计组合逻辑电路 ······  | 190        |

| 4.9 组合逻辑电路中的竞争-冒险 ······     | 194        |

| 4.9.1 竞争-冒险现象及其成因 ······     | 194        |

| 4.9.2 检查竞争-冒险现象的方法 ······    | 196        |

| 4.9.3 消除竞争-冒险现象的方法 ······    | 197        |

| 本章小结 ······                  | 199        |

| 习题 ······                    | 200        |

| <br>                         |            |

| <b>第五章 半导体存储电路 ······</b>    | <b>207</b> |

| 5.1 概述 ······                | 207        |

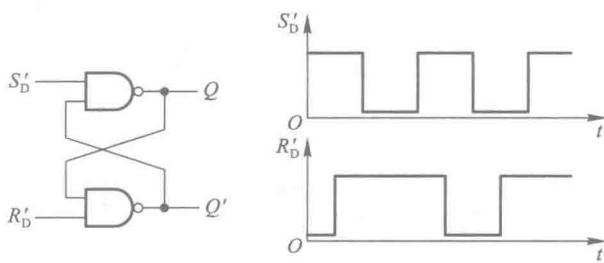

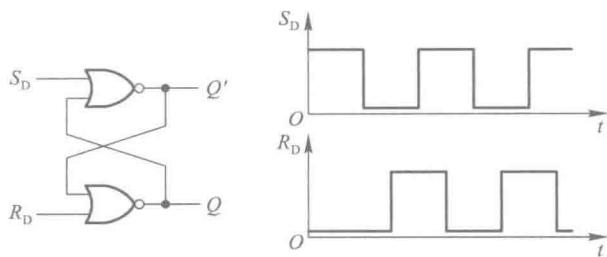

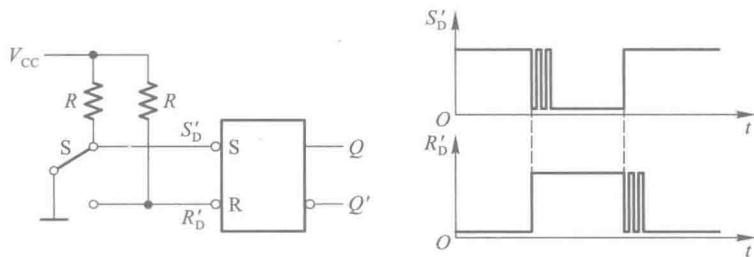

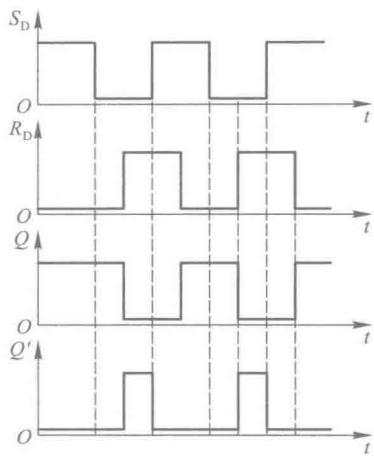

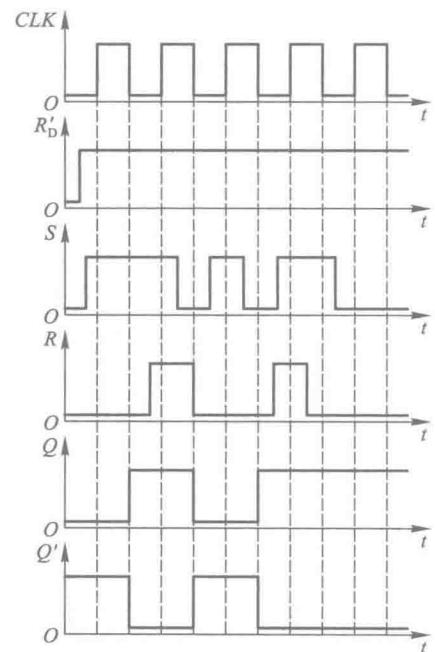

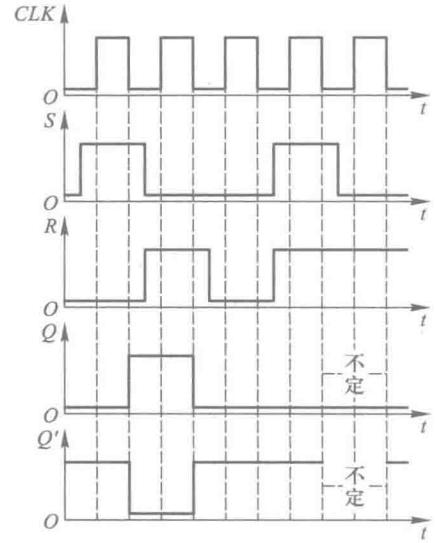

| 5.2 SR 锁存器 ······            | 208        |

| 5.3 触发器 ······               | 210        |

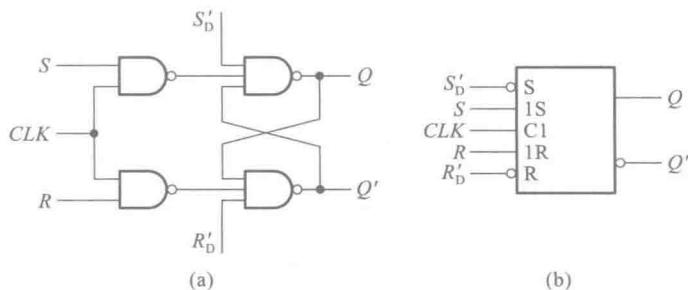

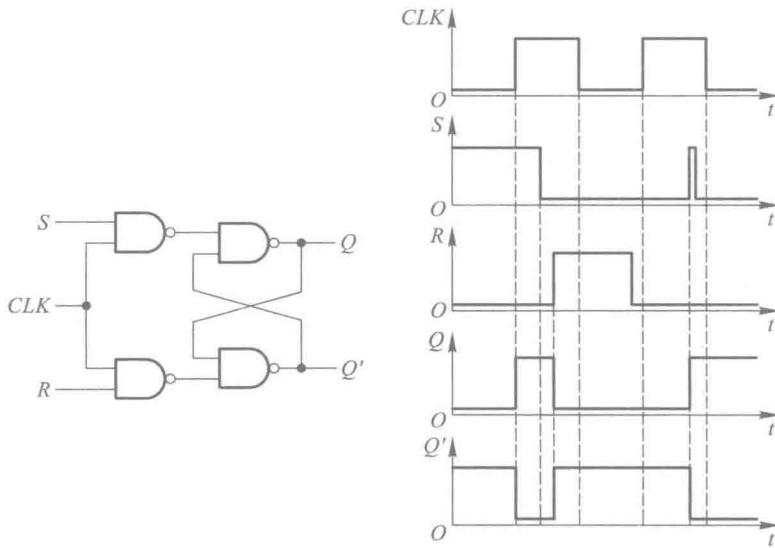

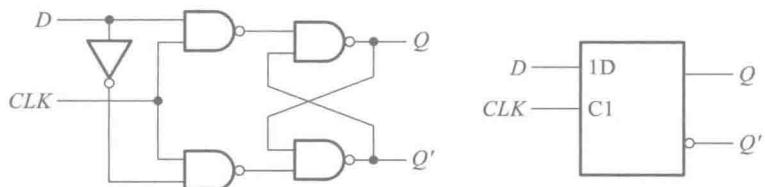

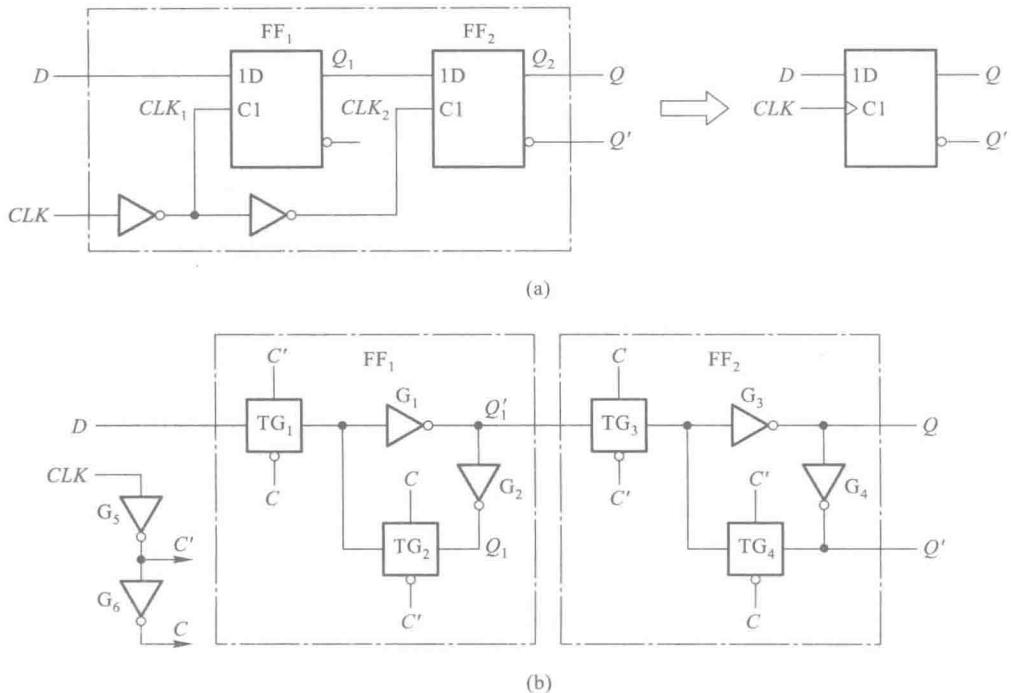

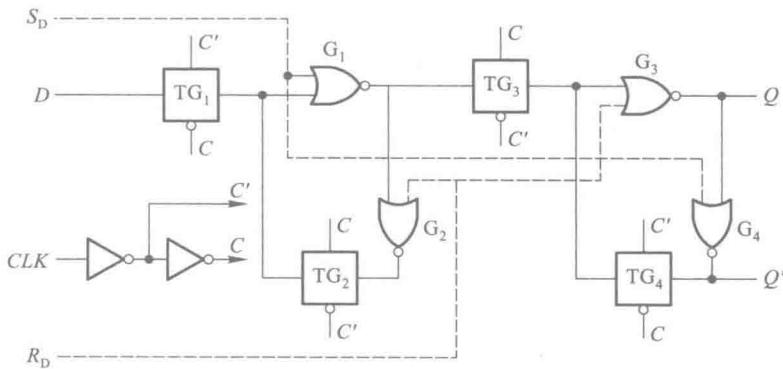

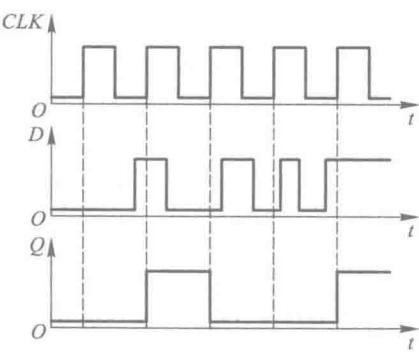

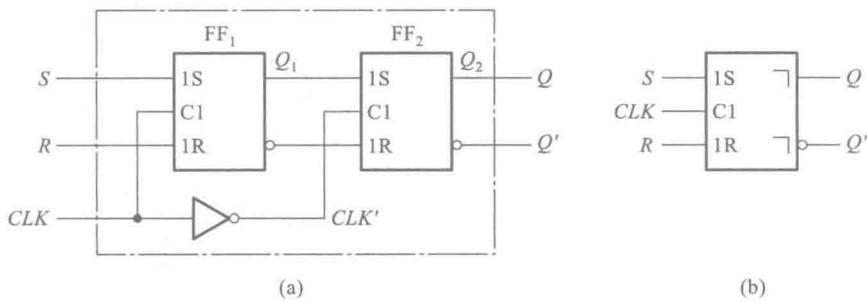

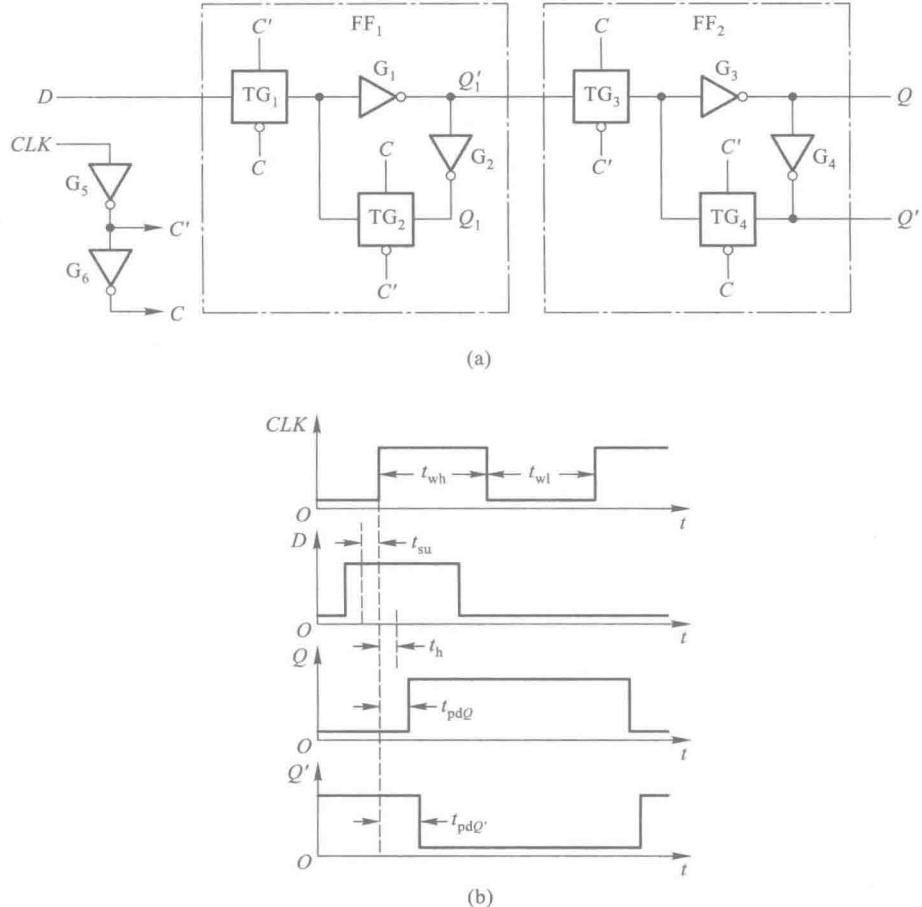

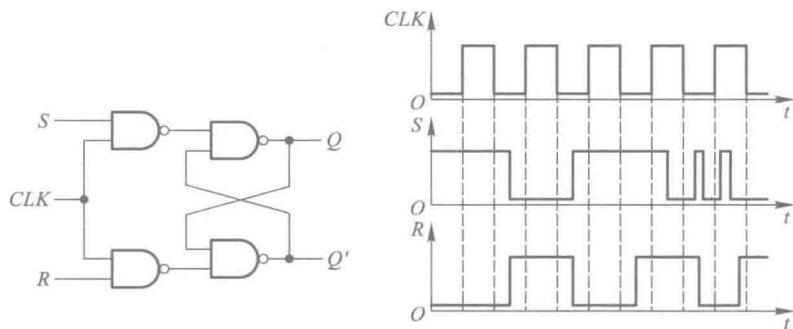

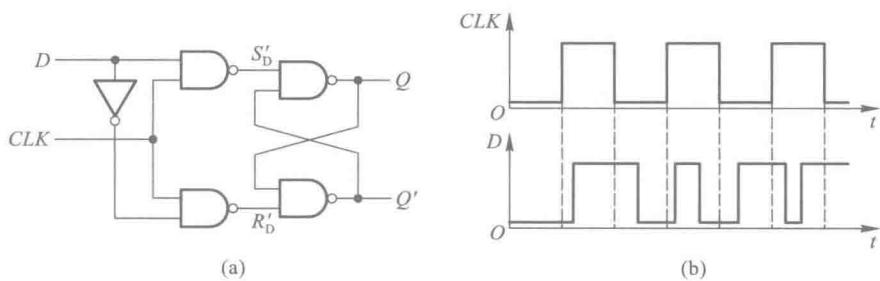

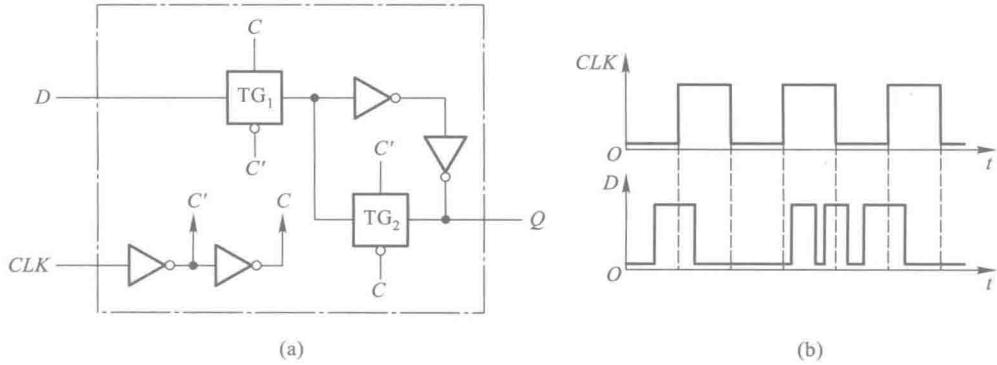

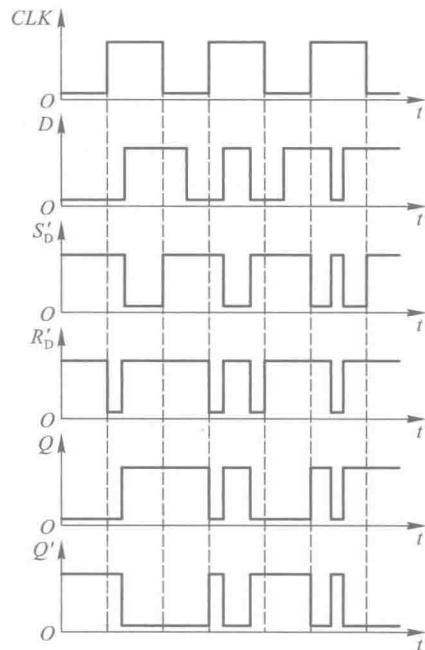

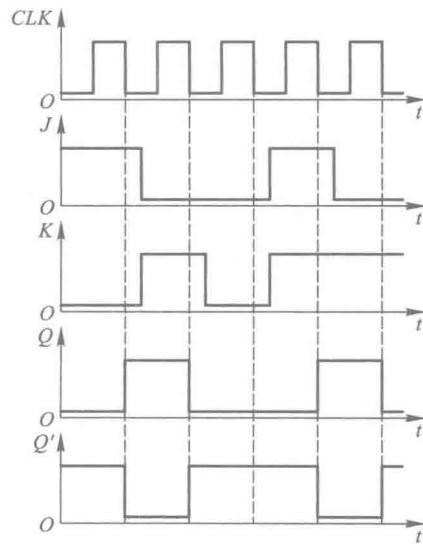

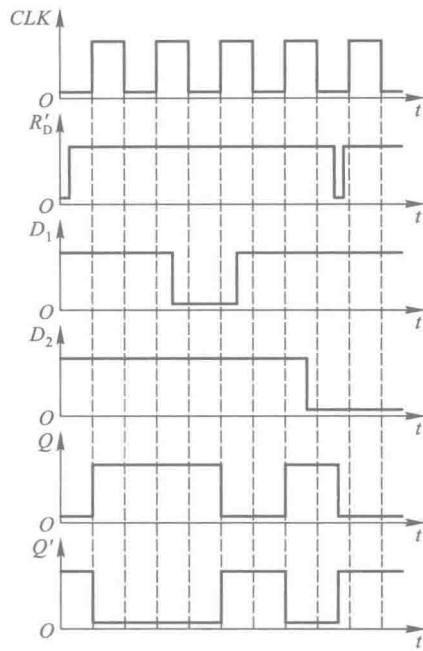

| 5.3.1 电平触发的触发器 ······        | 211        |

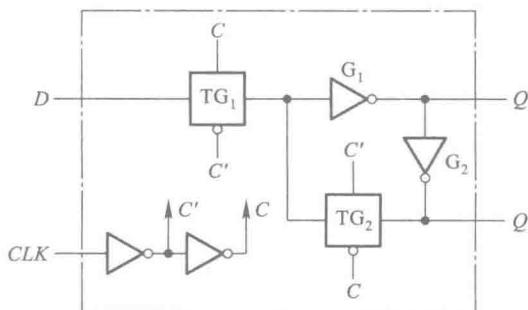

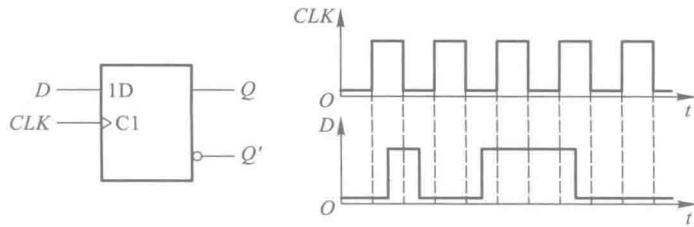

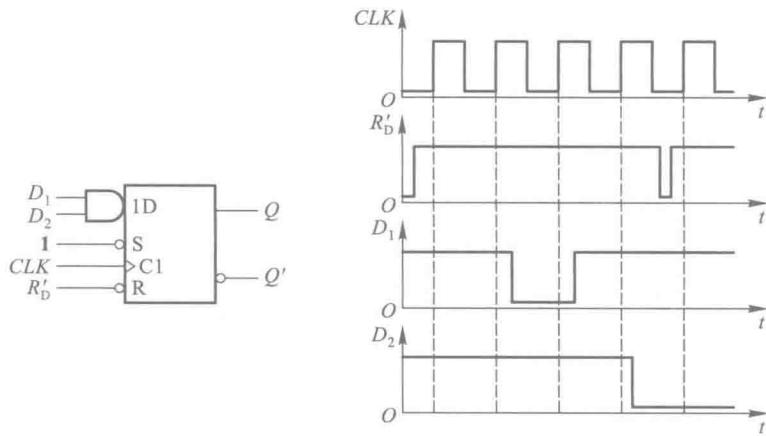

| 5.3.2 边沿触发的触发器 ······        | 215        |

| 5.3.3 脉冲触发的触发器 ······        | 218        |

| 5.3.4 触发器按逻辑功能的分类 ······     | 224        |

| 5.3.5 触发器的动态特性 ······        | 227        |

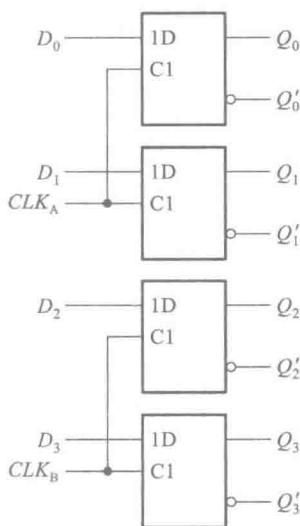

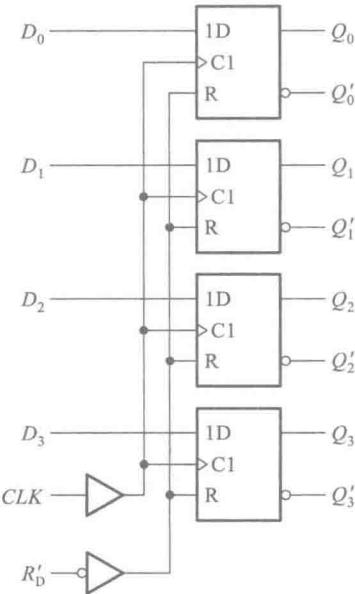

| 5.4 寄存器 ······               | 229        |

| 5.5 存储器 ······               | 230        |

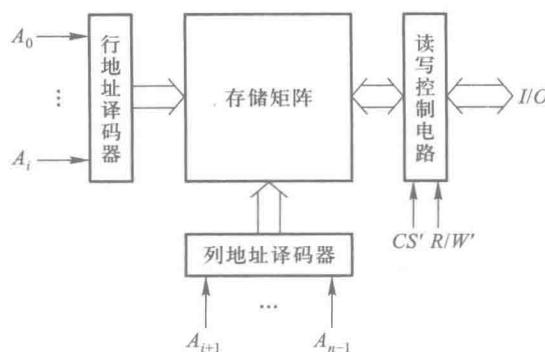

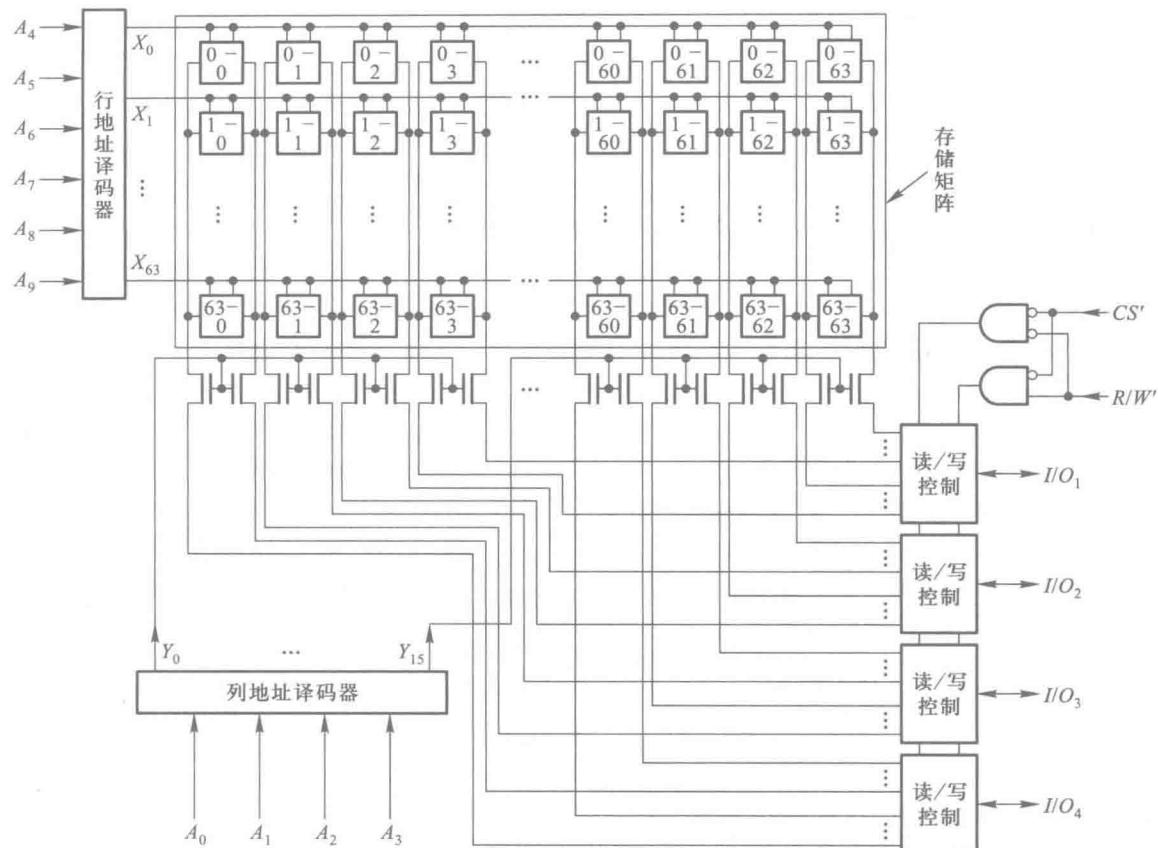

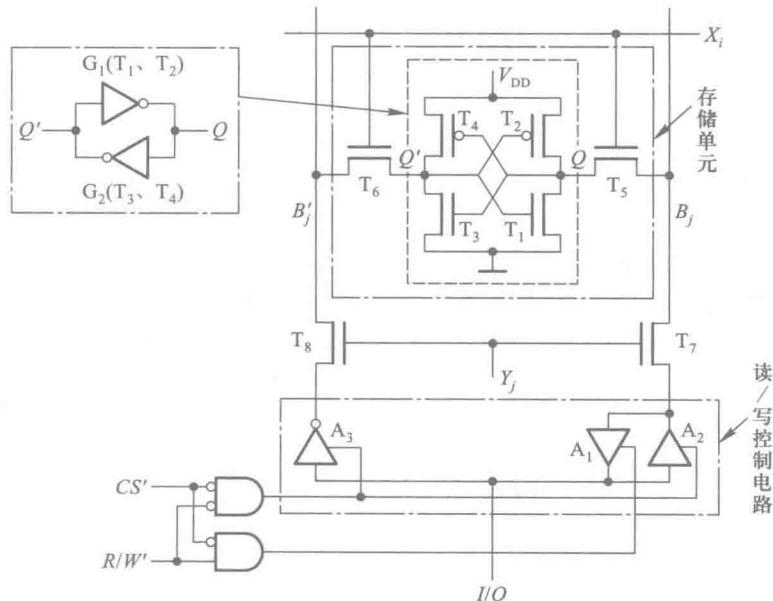

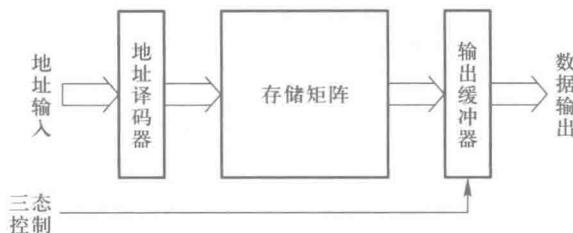

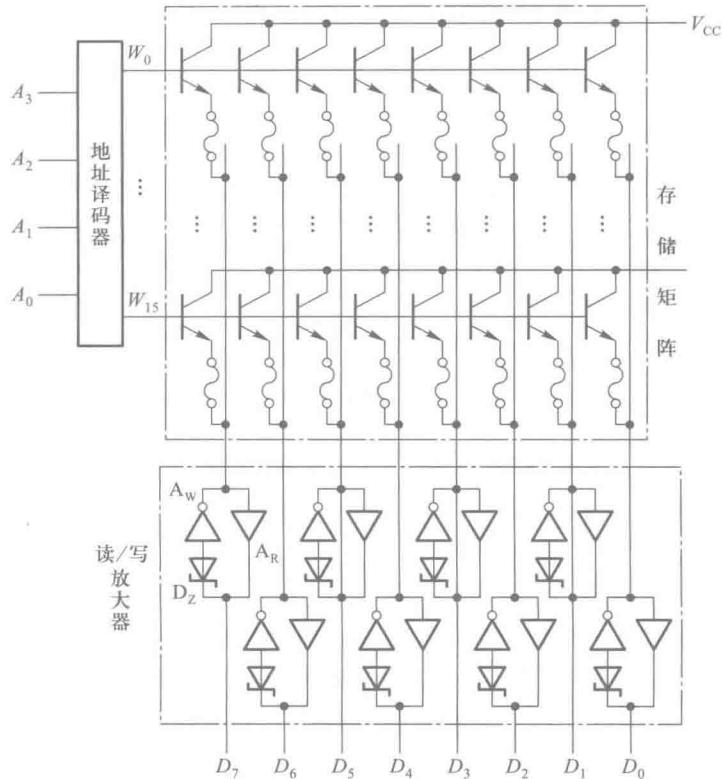

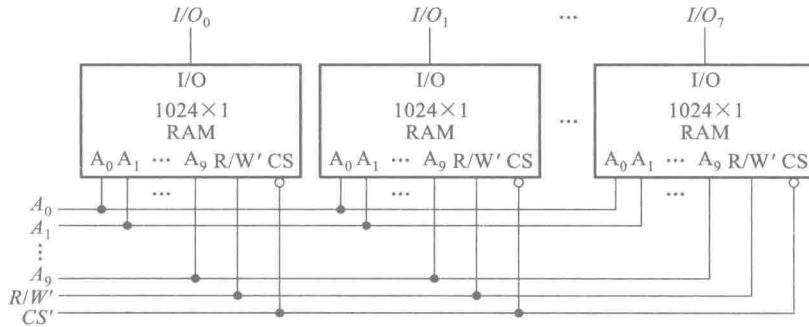

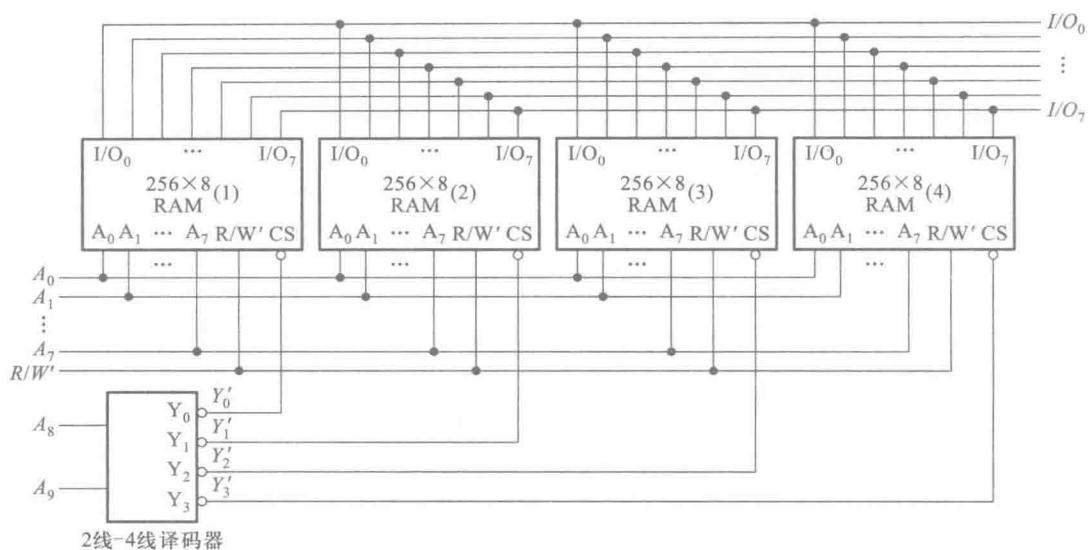

| 5.5.1 静态随机存储器(SRAM) ······   | 231        |

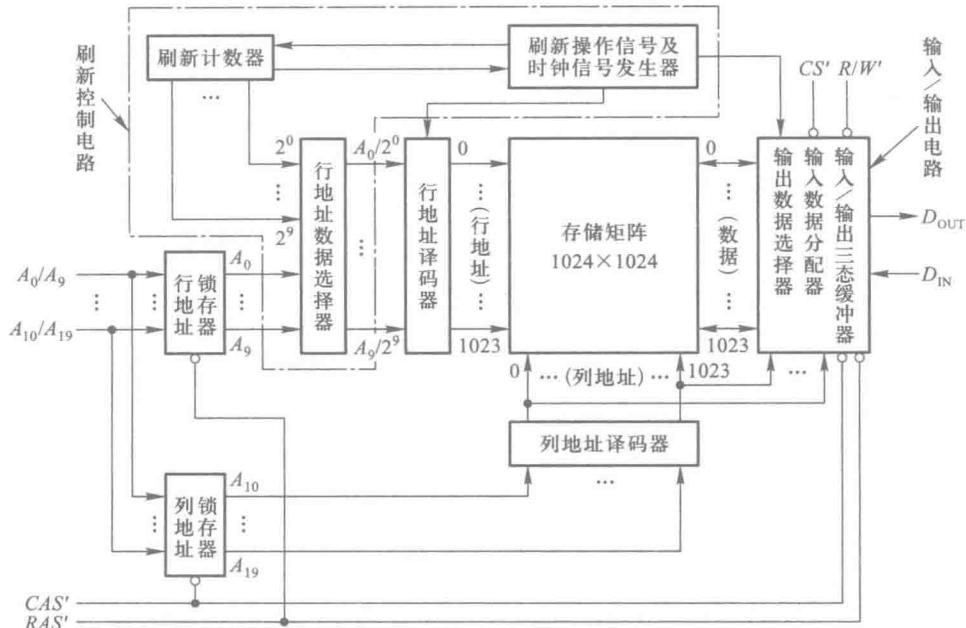

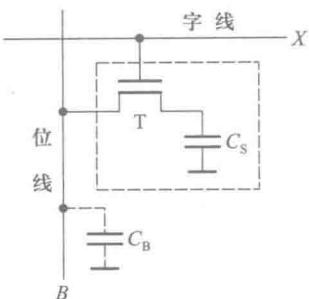

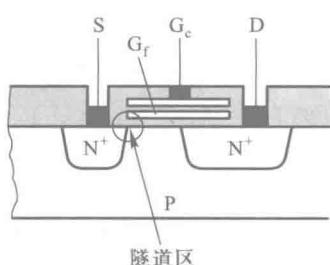

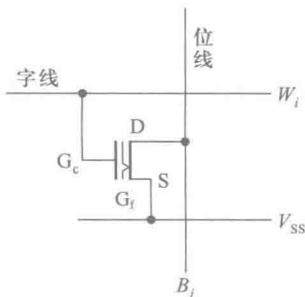

| * 5.5.2 动态随机存储器(DRAM) ······ | 234        |

|                                           |            |

|-------------------------------------------|------------|

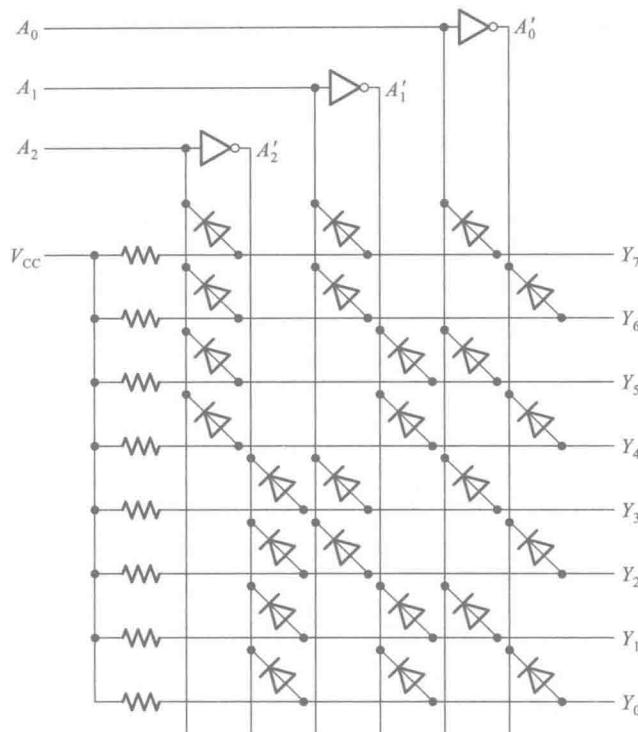

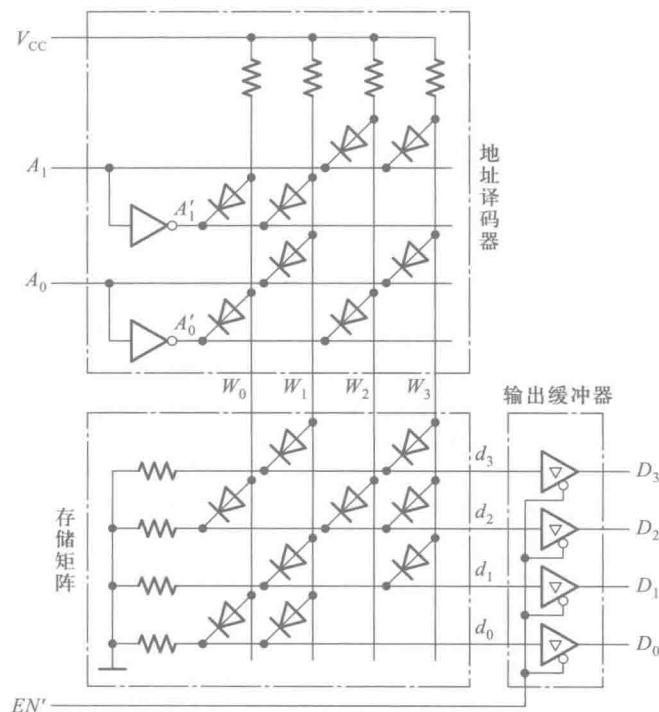

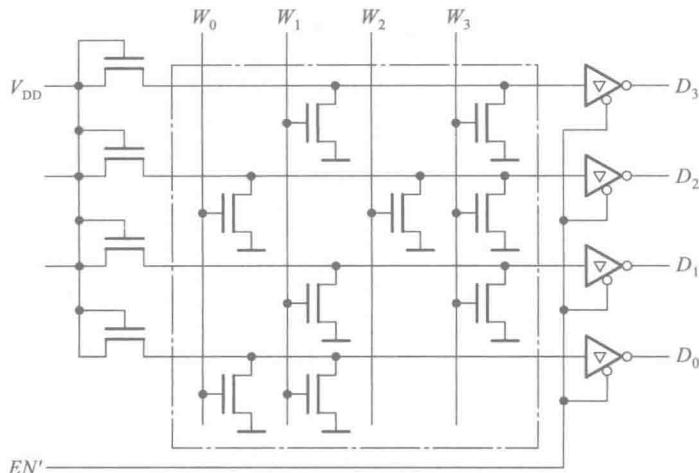

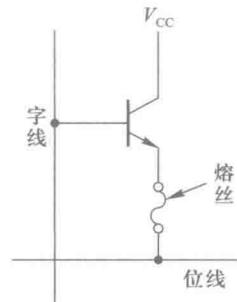

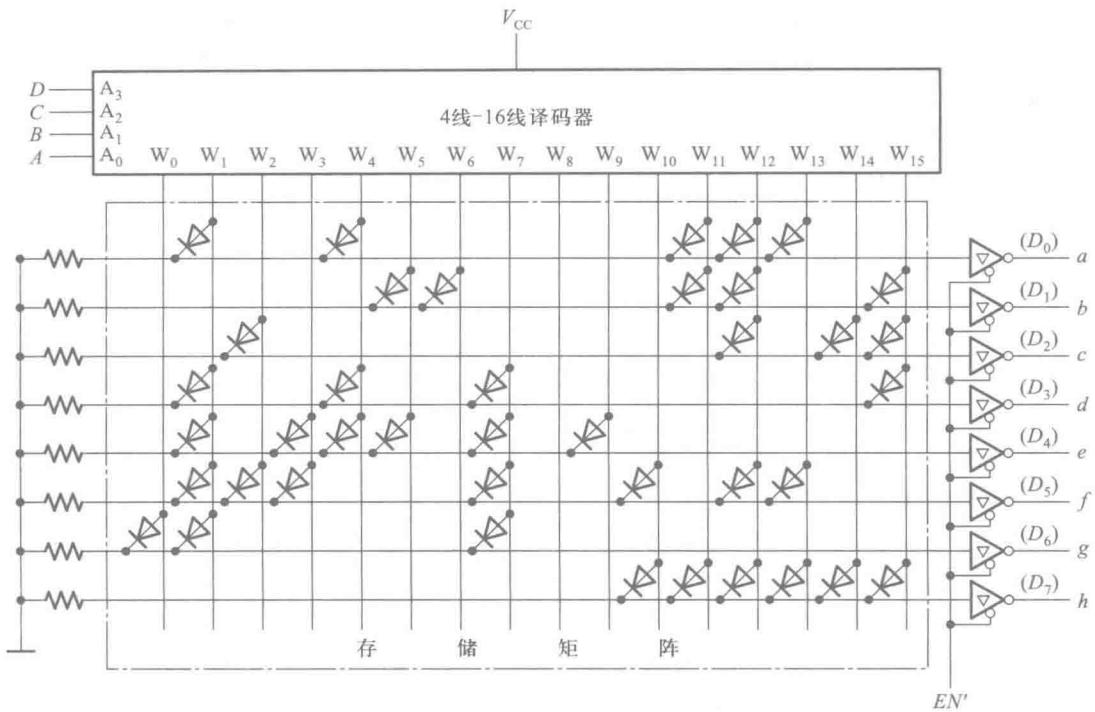

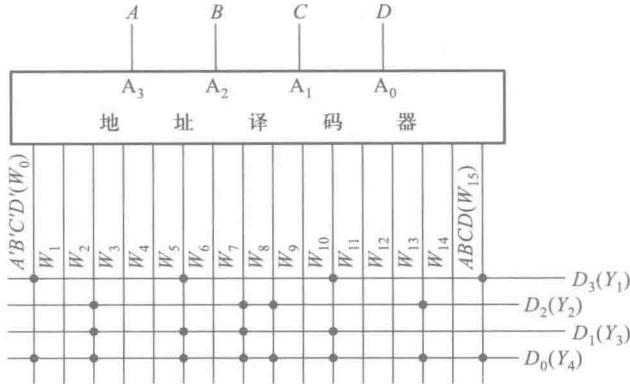

| 5.5.3 只读存储器(ROM) .....                    | 236        |

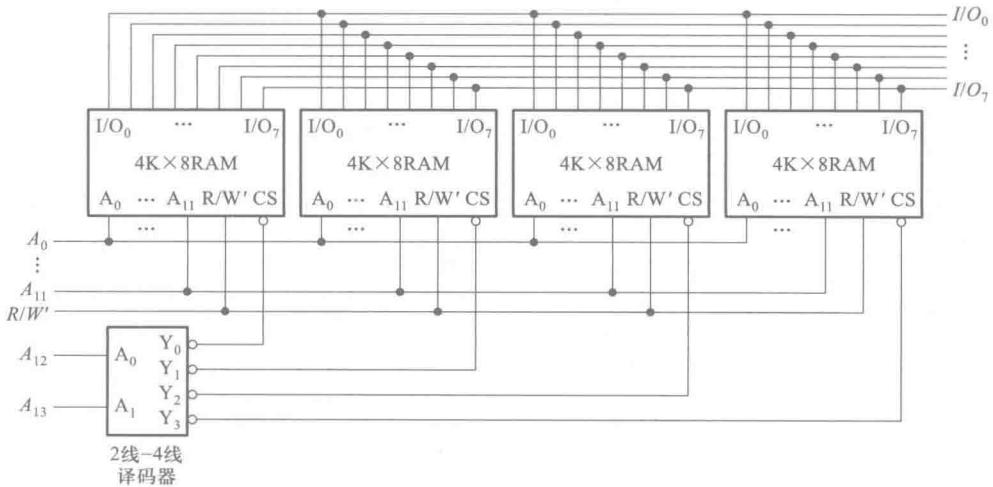

| 5.5.4 存储器容量的扩展 .....                      | 242        |

| 5.5.5 用存储器实现组合逻辑函数.....                   | 244        |

| 本章小结 .....                                | 249        |

| 习题 .....                                  | 250        |

| <b>第六章 时序逻辑电路 .....</b>                   | <b>261</b> |

| 6.1 概述 .....                              | 261        |

| 6.2 时序逻辑电路的分析方法 .....                     | 263        |

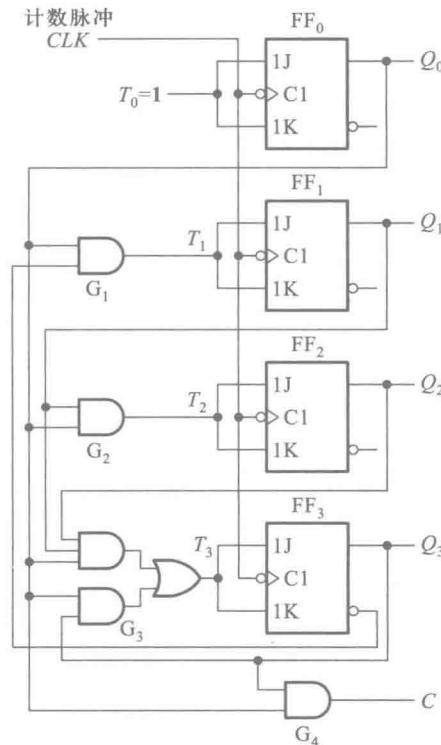

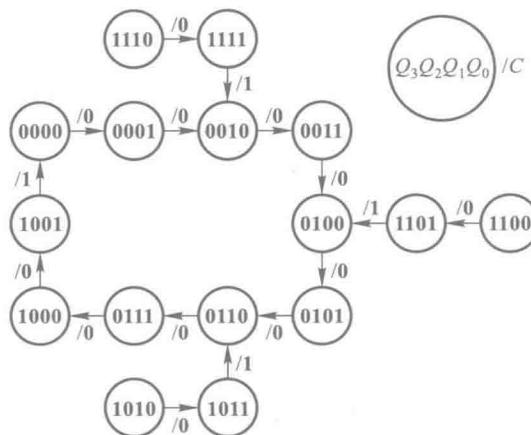

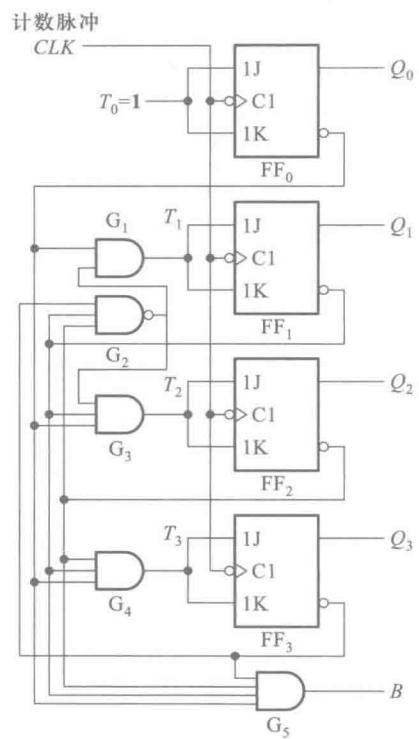

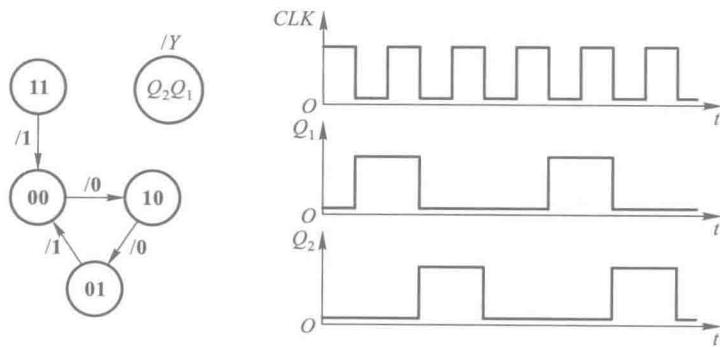

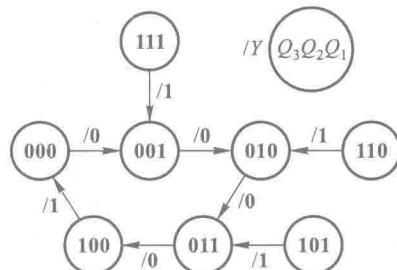

| 6.2.1 同步时序逻辑电路的分析方法 .....                 | 263        |

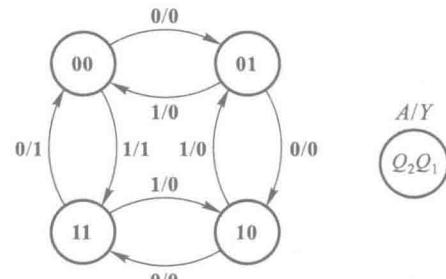

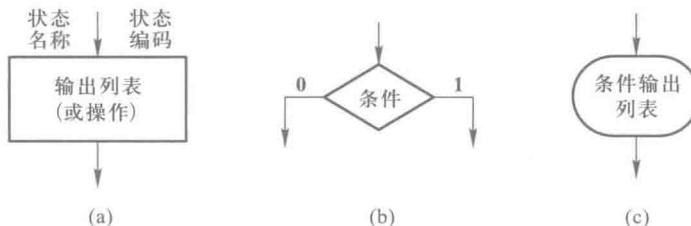

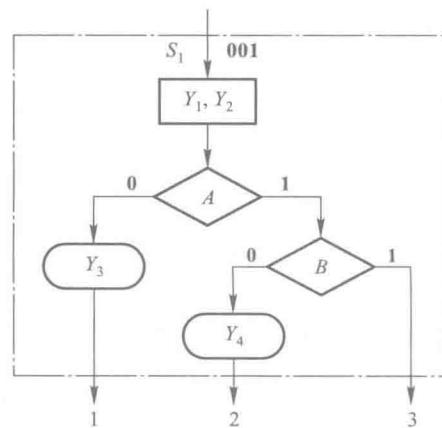

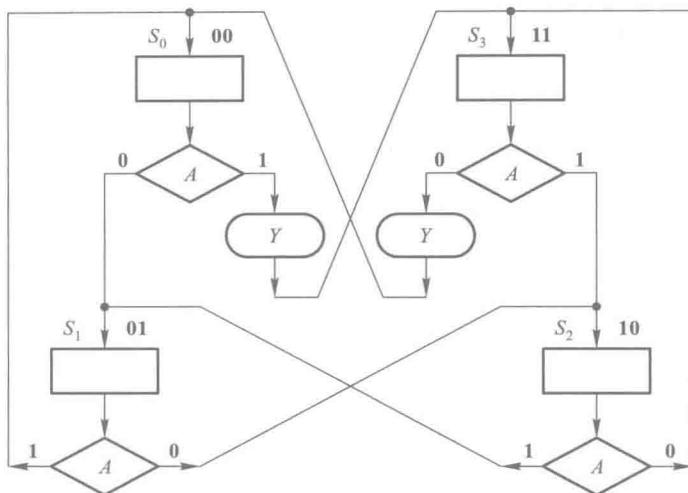

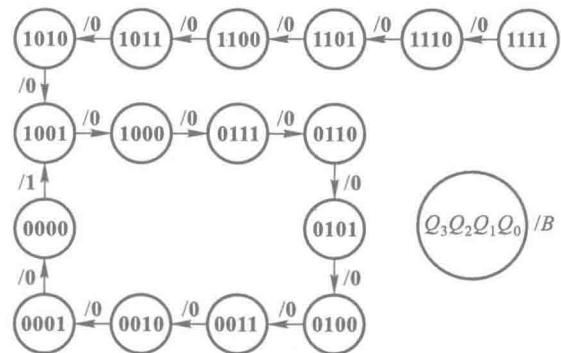

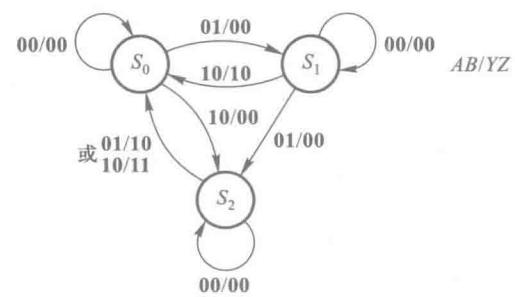

| 6.2.2 时序逻辑电路的状态转换表、状态转换图、状态机流程图和时序图 ..... | 264        |

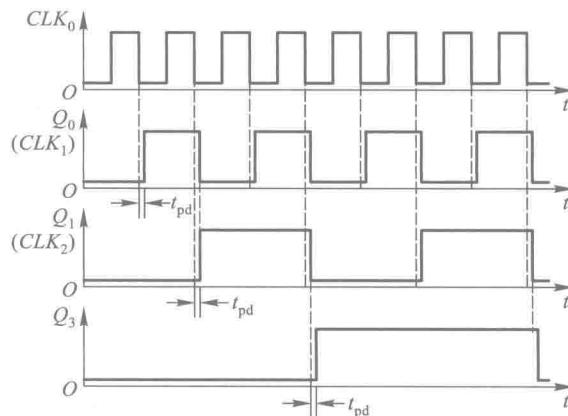

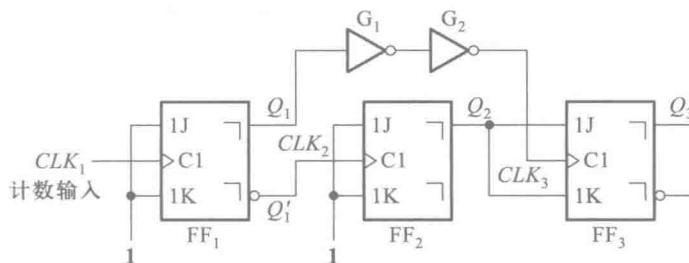

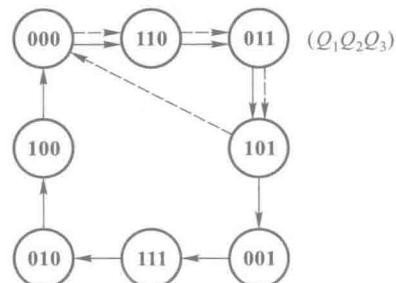

| * 6.2.3 异步时序逻辑电路的分析方法 .....               | 270        |

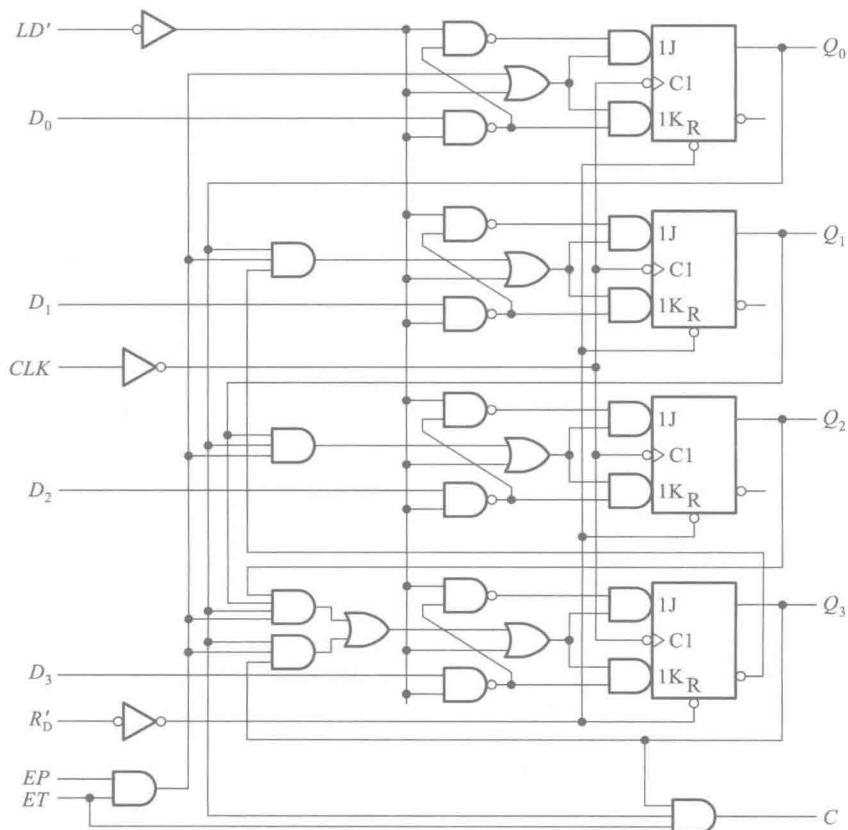

| 6.3 若干常用的时序逻辑电路 .....                     | 271        |

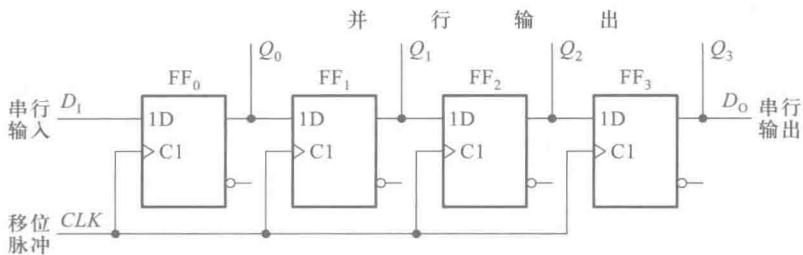

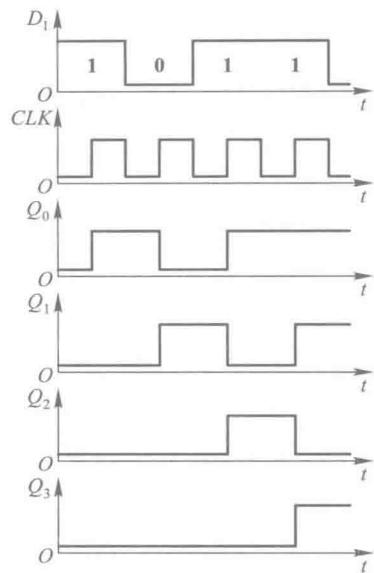

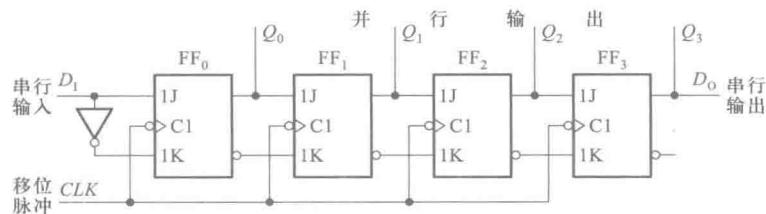

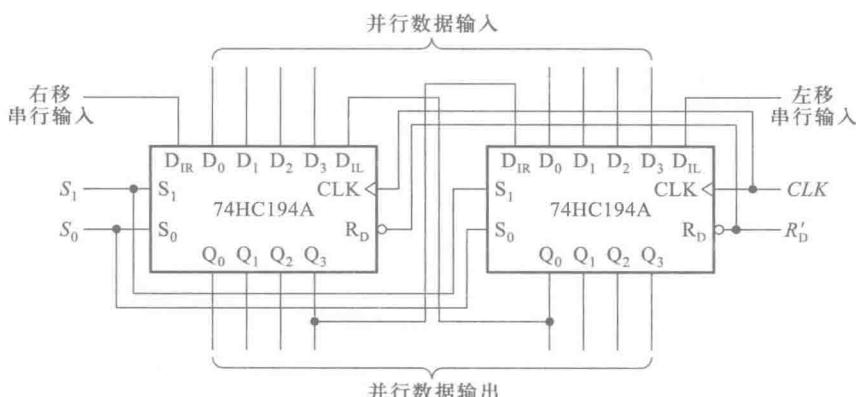

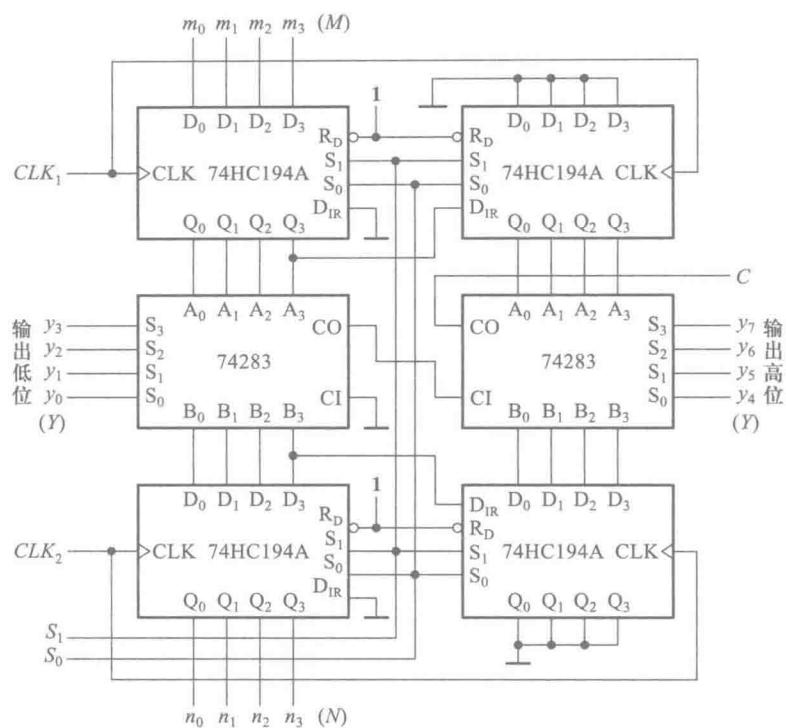

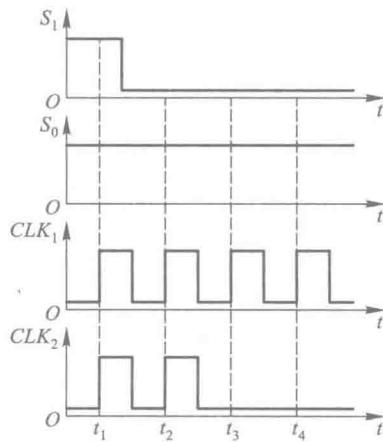

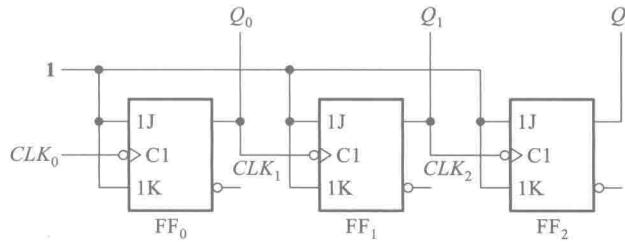

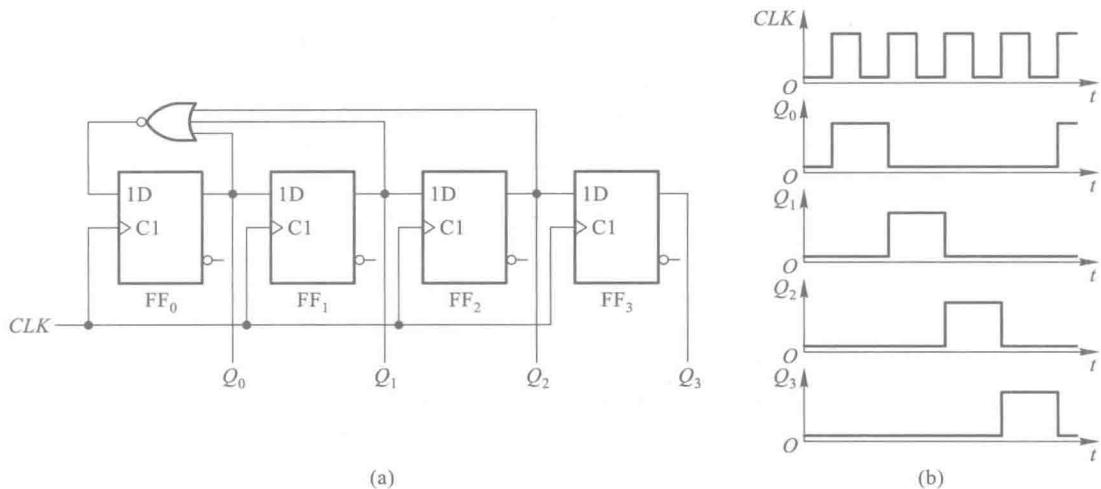

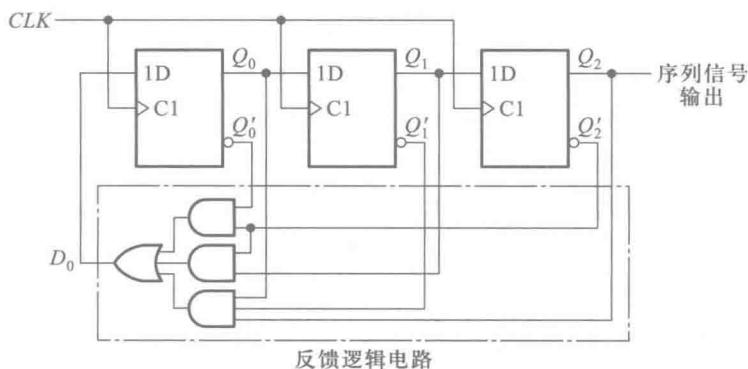

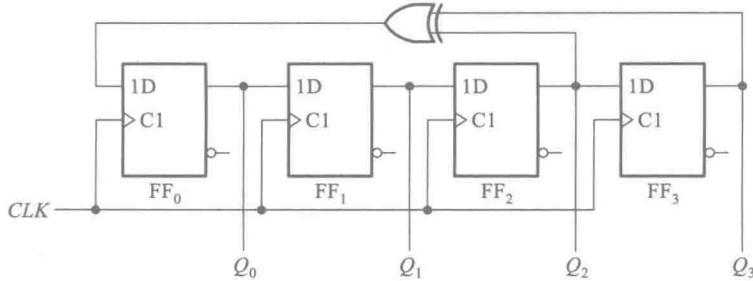

| 6.3.1 移位寄存器.....                          | 271        |

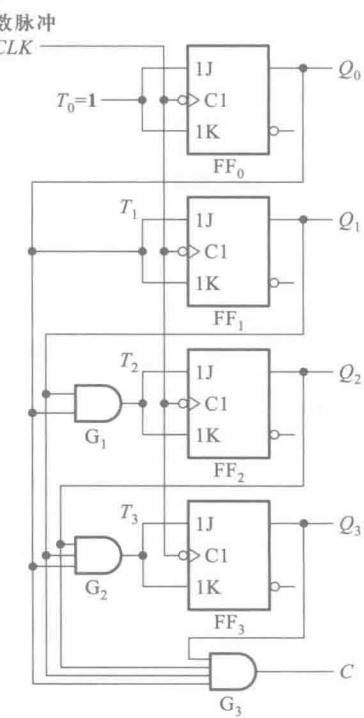

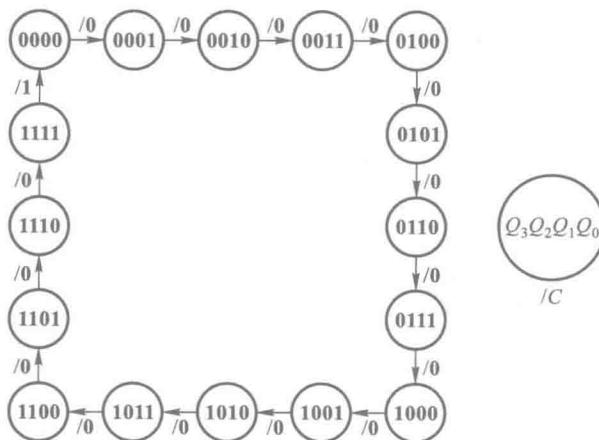

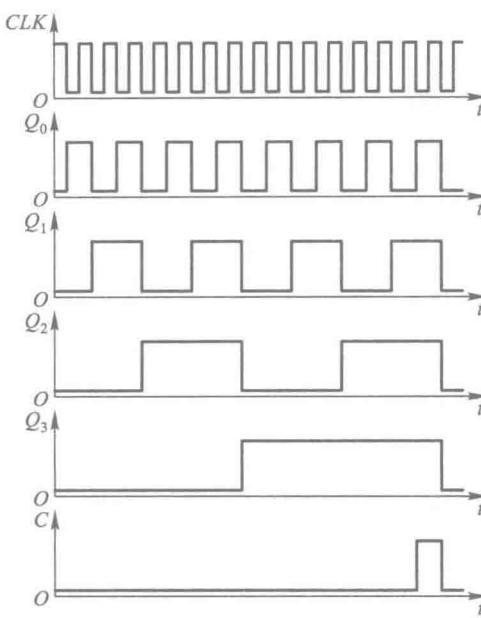

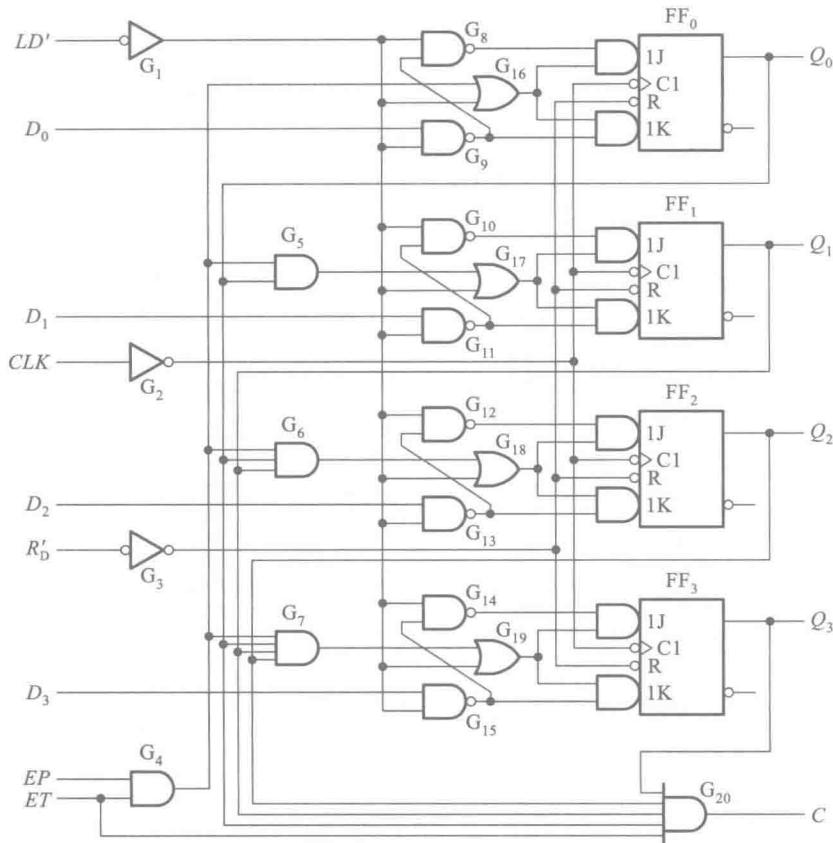

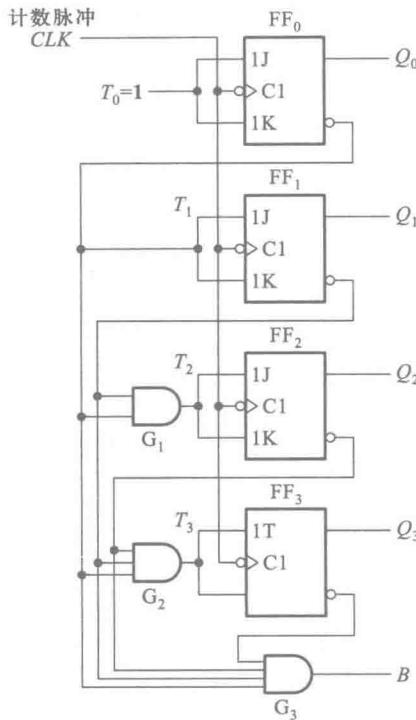

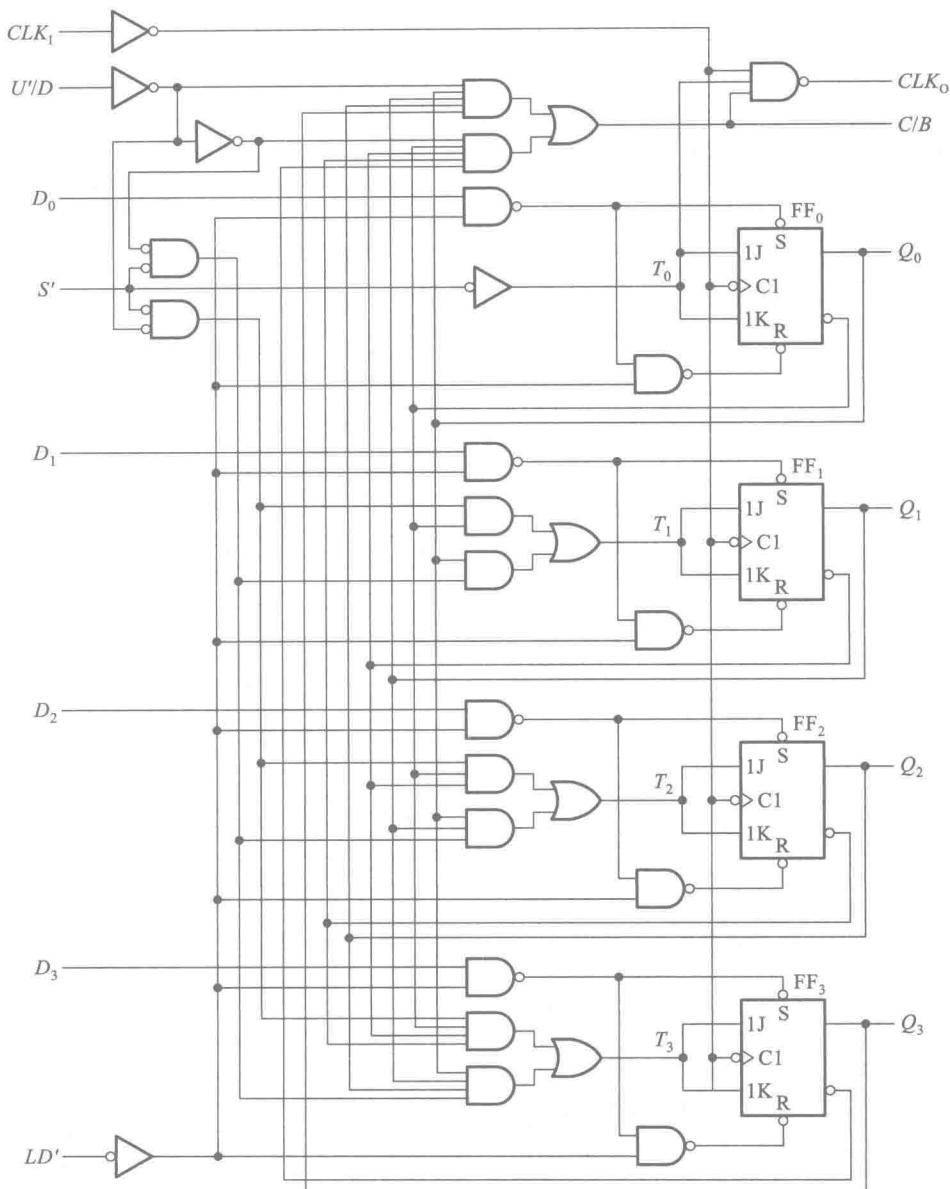

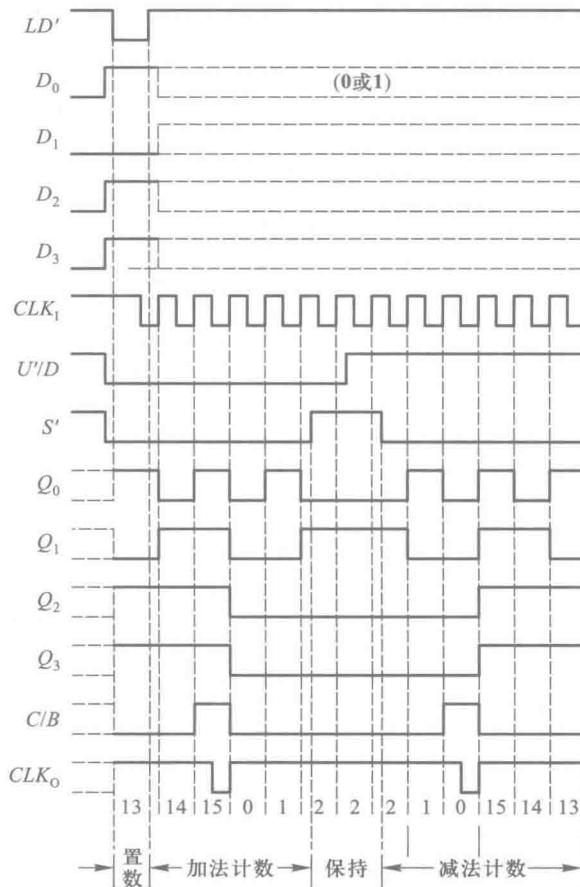

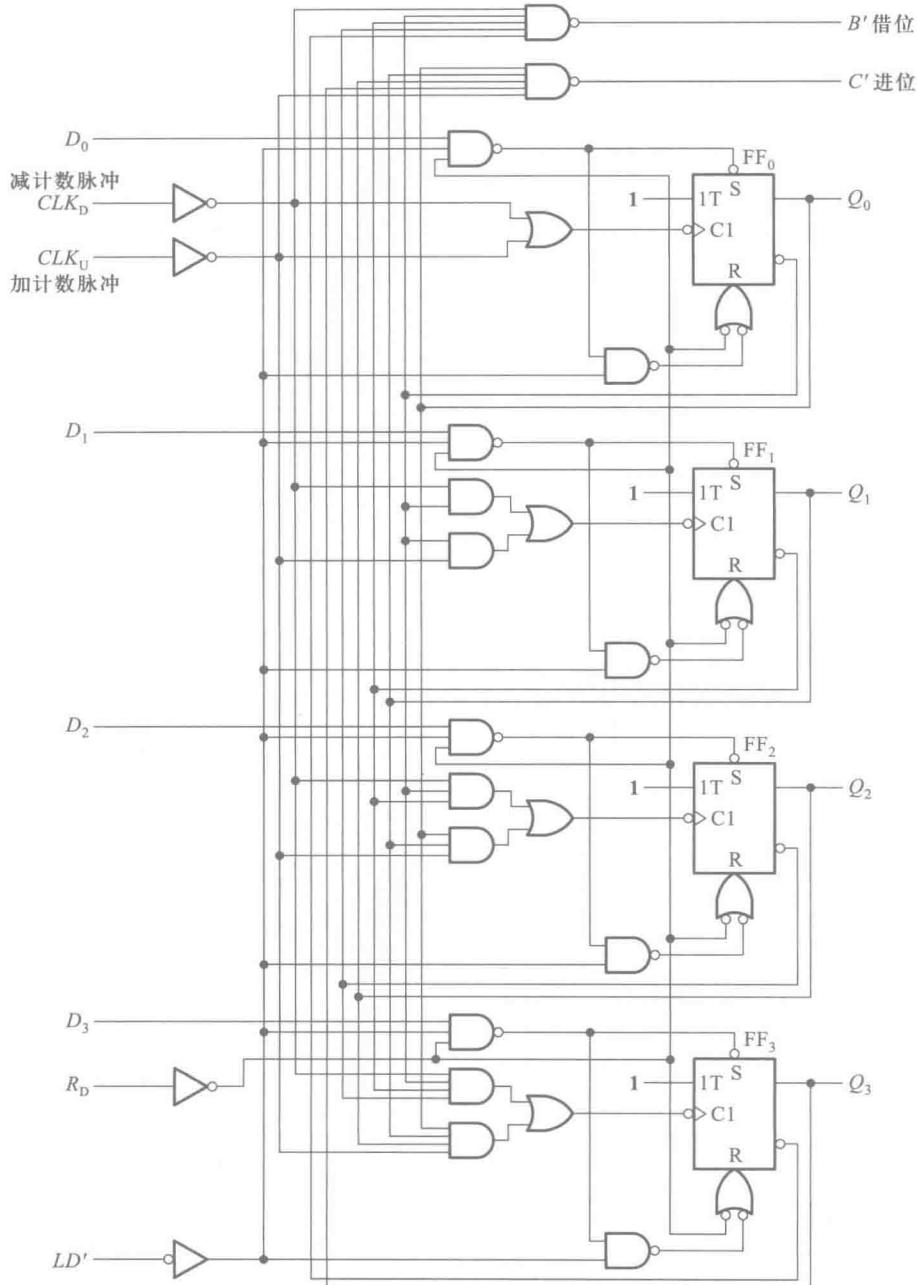

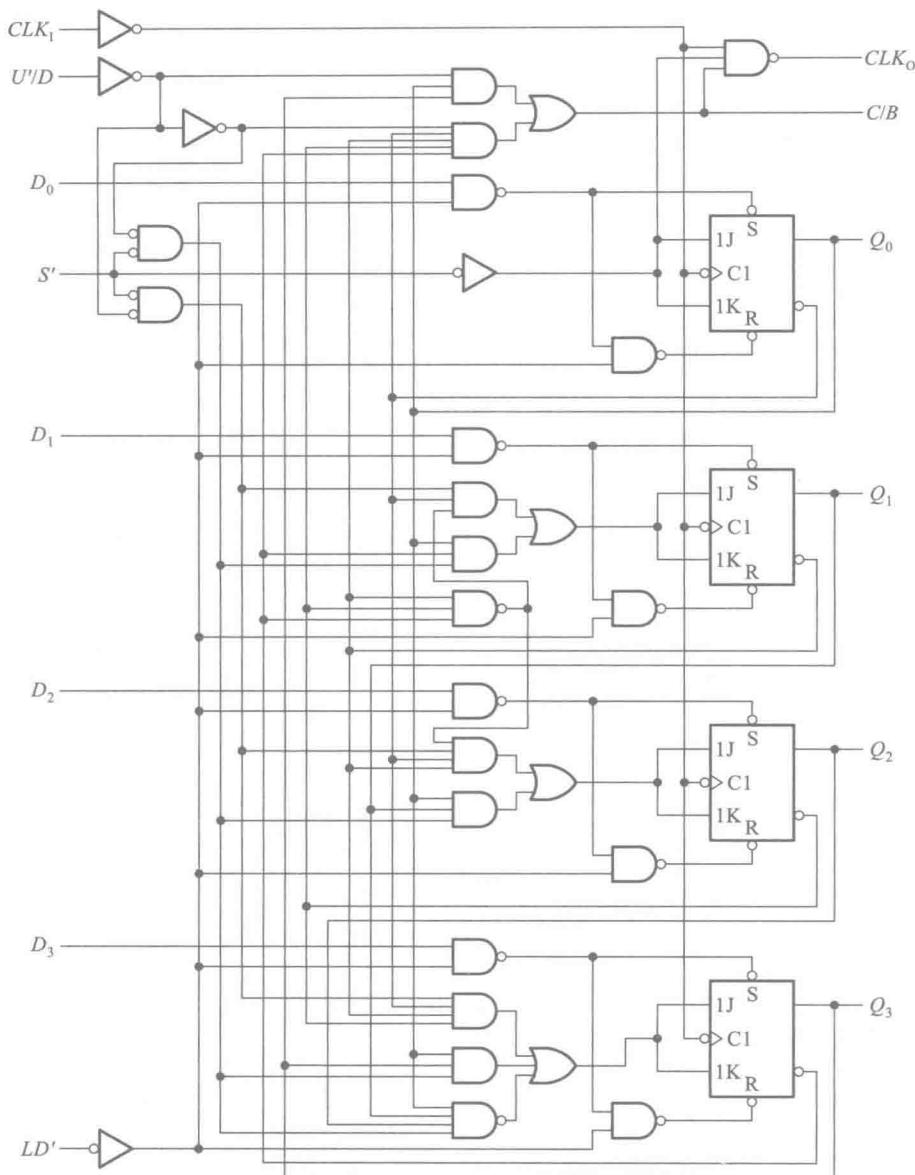

| 6.3.2 计数器 .....                           | 275        |

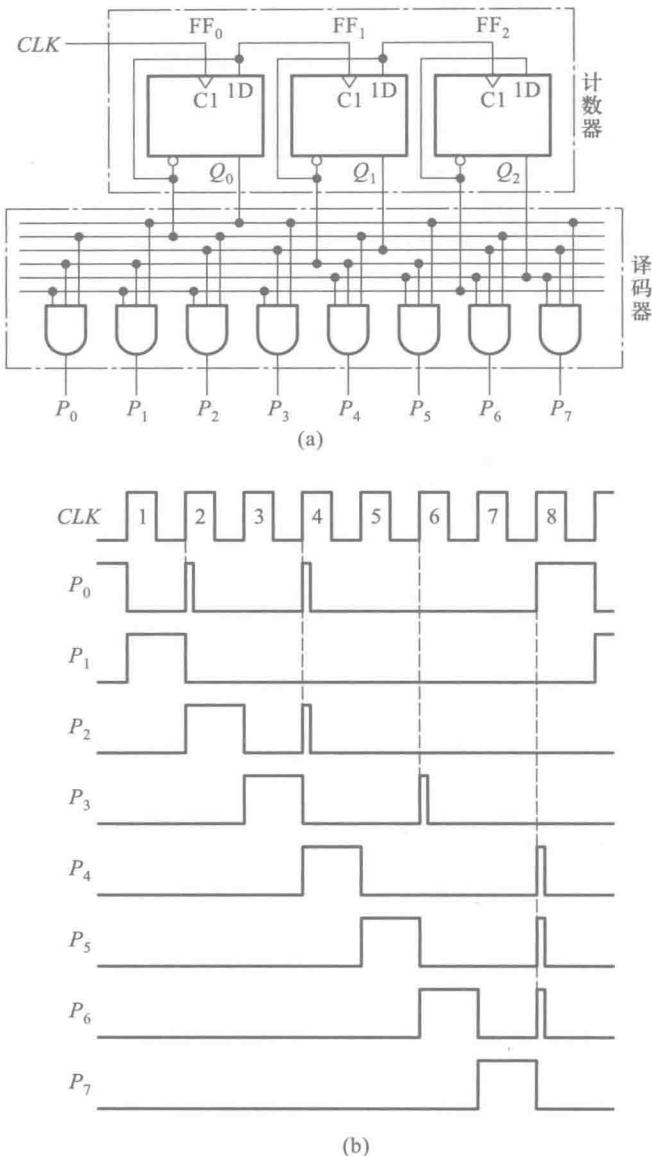

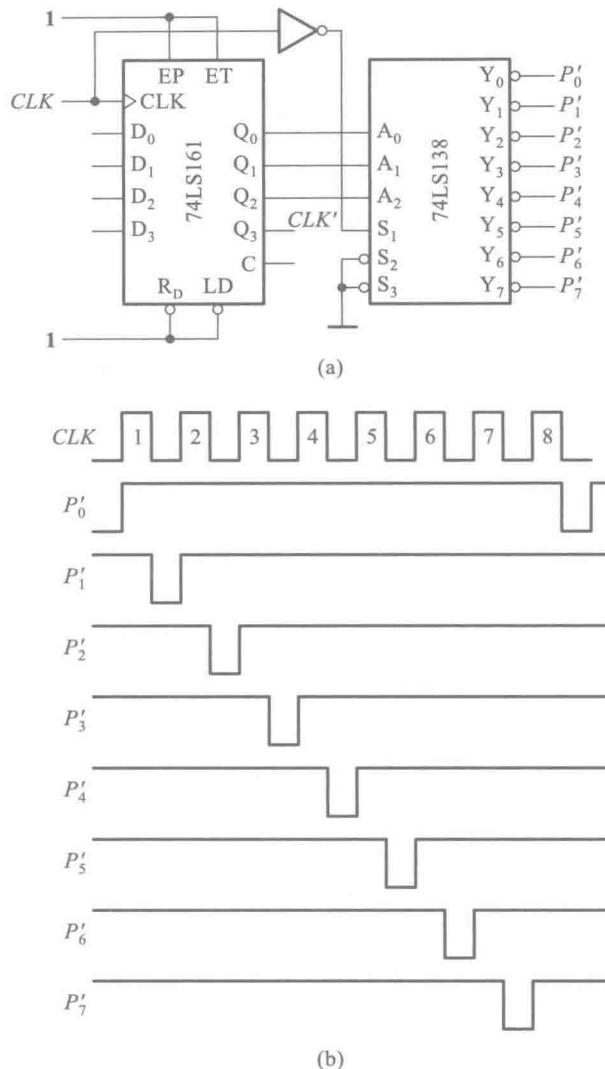

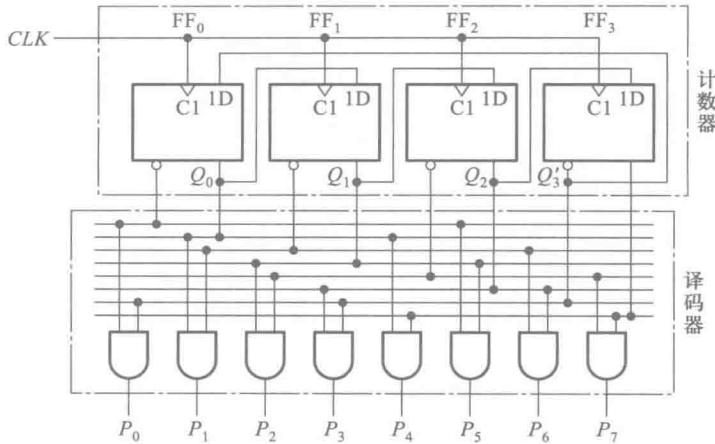

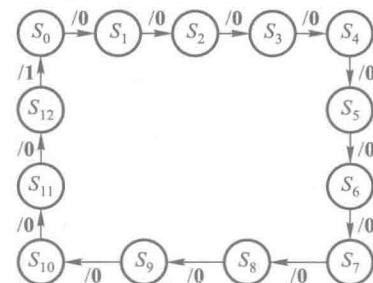

| 6.3.3 顺序脉冲发生器 .....                       | 304        |

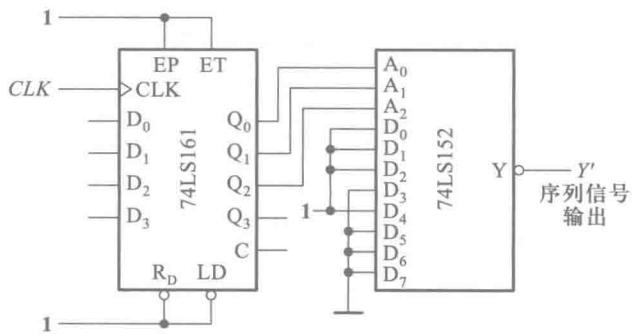

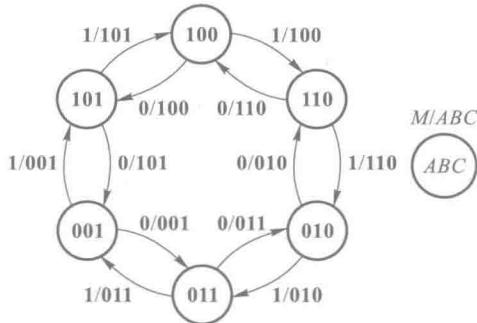

| 6.3.4 序列信号发生器 .....                       | 308        |

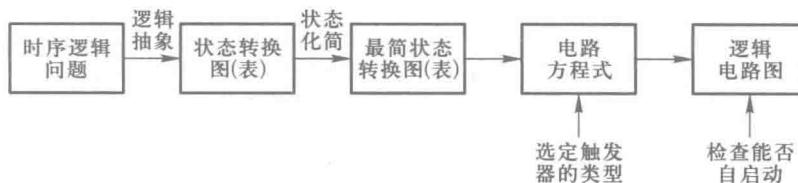

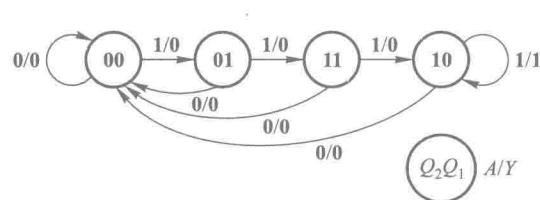

| 6.4 时序逻辑电路的设计方法 .....                     | 310        |

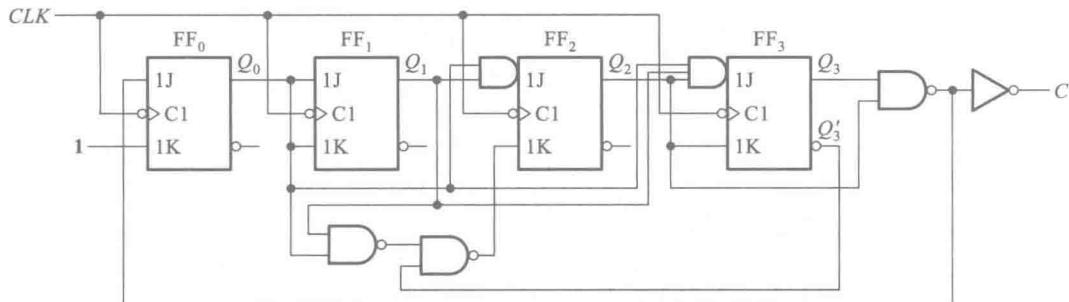

| 6.4.1 同步时序逻辑电路的设计方法 .....                 | 310        |

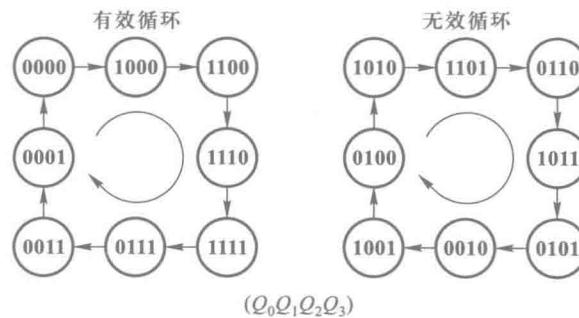

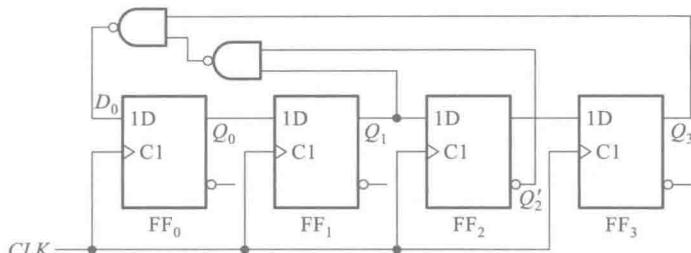

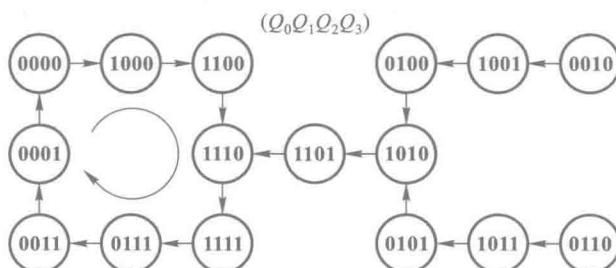

| 6.4.2 时序逻辑电路的自启动设计.....                   | 320        |

| * 6.4.3 异步时序逻辑电路的设计方法 .....               | 324        |

| * 6.4.4 复杂时序逻辑电路的设计 .....                 | 328        |

| 6.5 用可编程逻辑器件实现同步时序逻辑电路 .....              | 330        |

| 6.5.1 可以实现时序逻辑电路的可编程逻辑器件 .....            | 330        |

| 6.5.2 用硬件描述语言 Verilog HDL 描述时序逻辑电路 .....  | 331        |

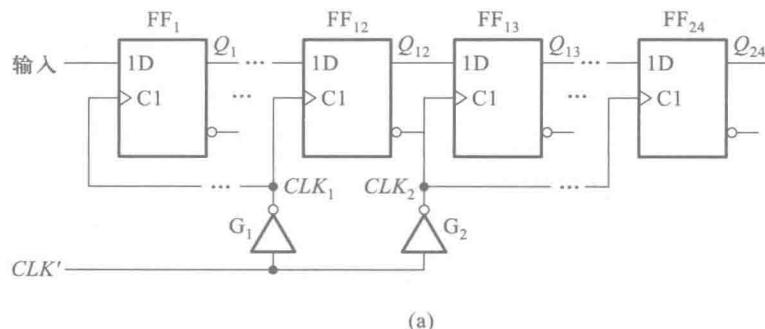

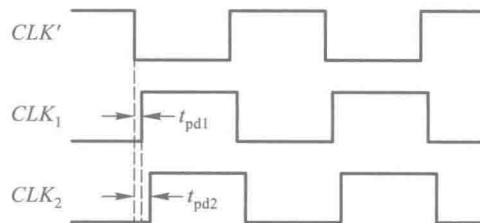

| 6.6 时序逻辑电路中的竞争-冒险现象 .....                 | 336        |

| 本章小结 .....                                | 340        |

| 习题 .....                                  | 341        |

| <b>第七章 脉冲波形的产生和整形电路 .....</b>             | <b>349</b> |

| 7.1 概述 .....                              | 349        |

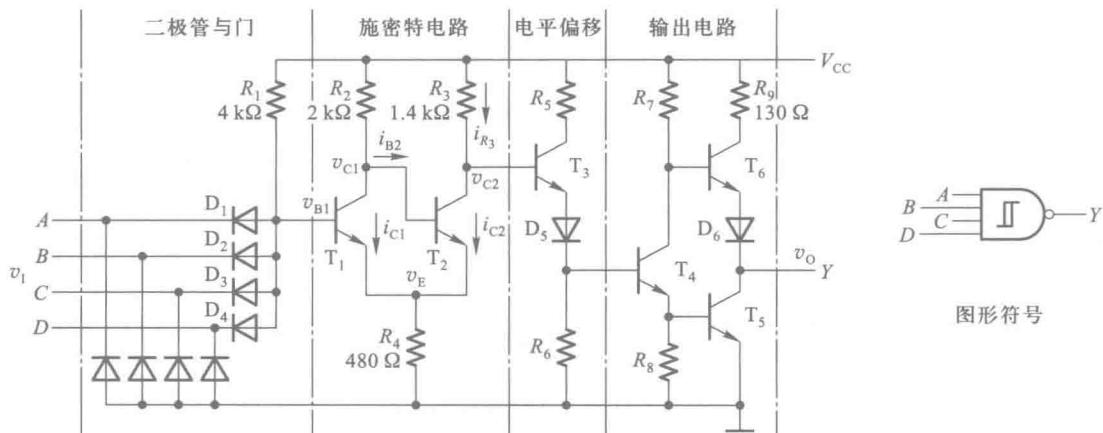

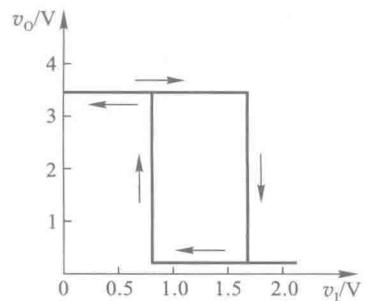

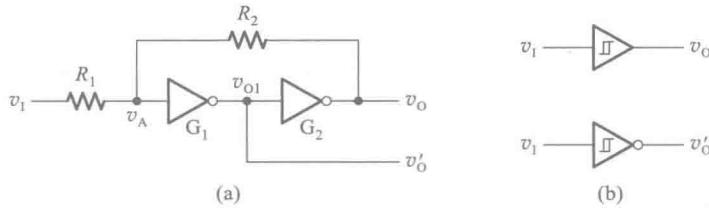

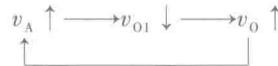

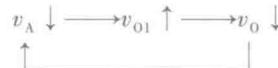

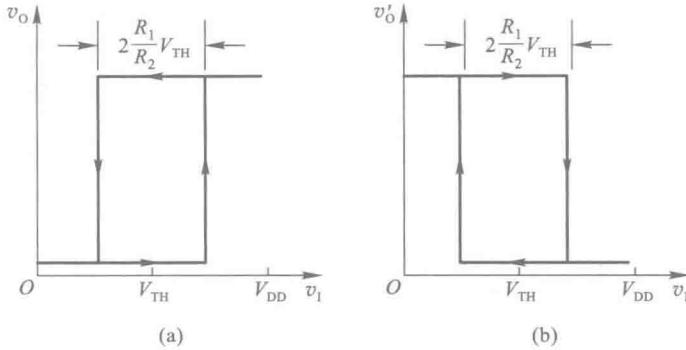

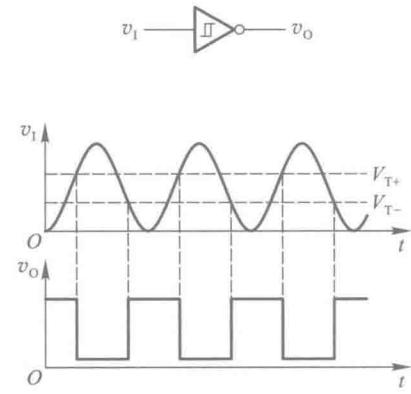

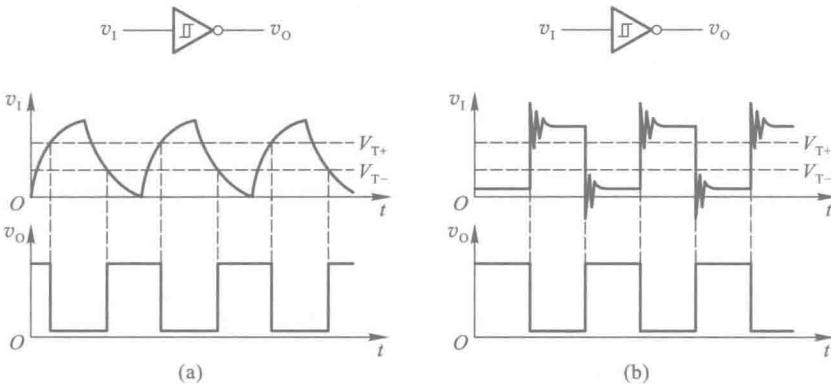

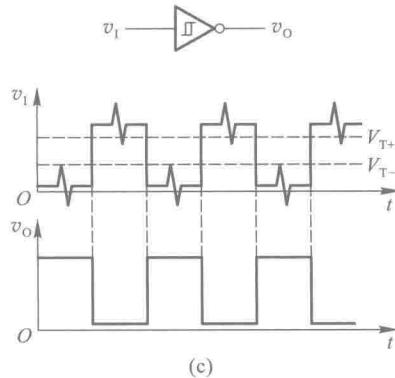

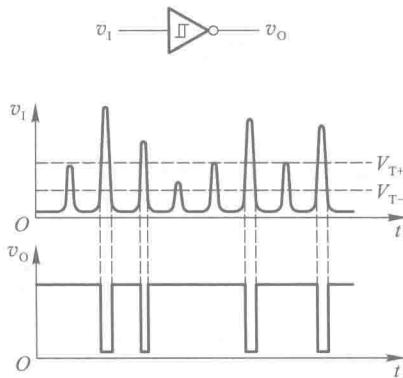

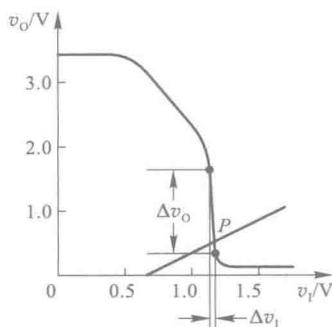

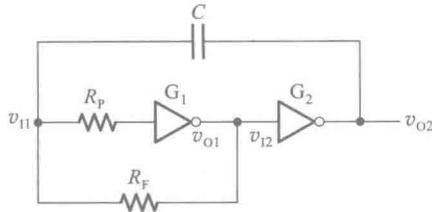

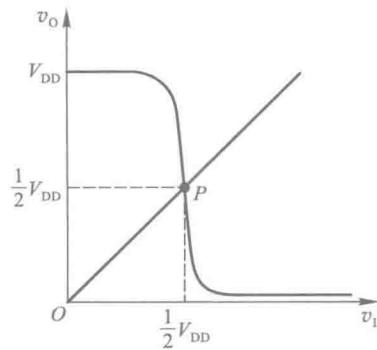

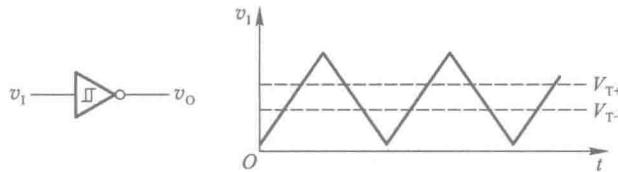

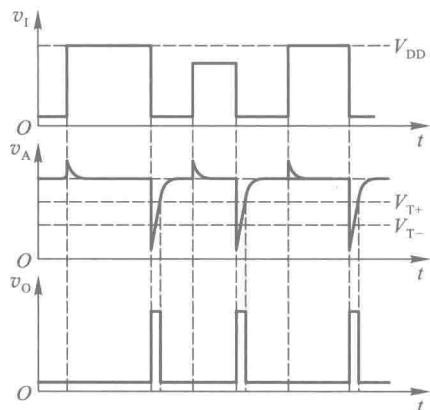

| 7.2 施密特触发电路.....                          | 350        |

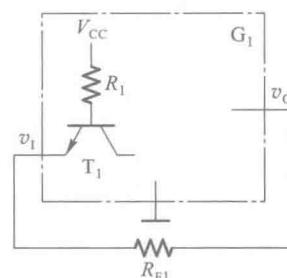

| 7.2.1 施密特触发电路的结构和工作原理 .....               | 350        |

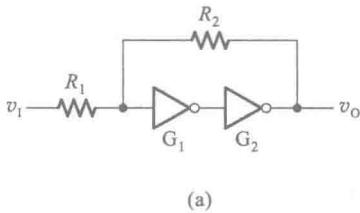

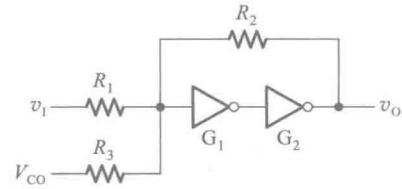

| 7.2.2 用门电路组成的施密特触发电路 .....                | 353        |

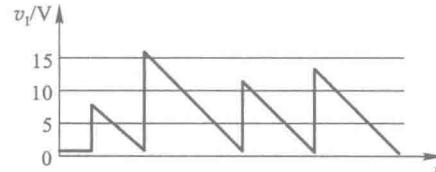

| 7.2.3 施密特触发电路的应用 .....                    | 355        |

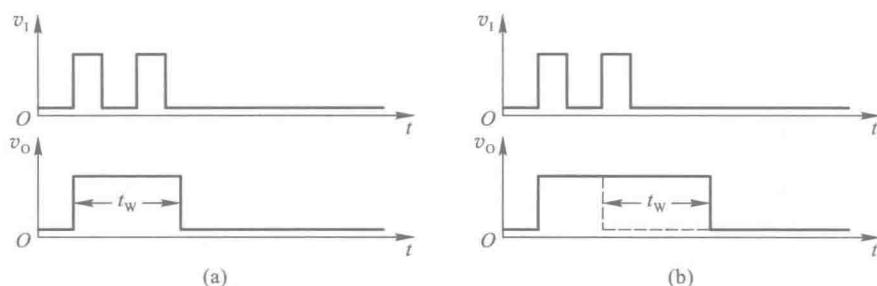

| 7.3 单稳态电路 .....                           | 357        |

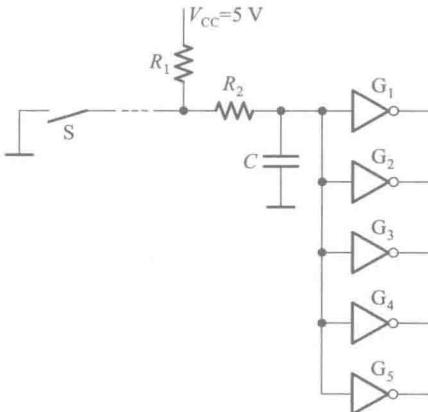

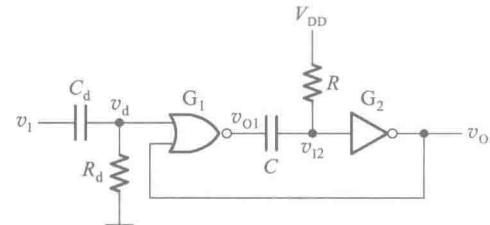

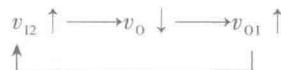

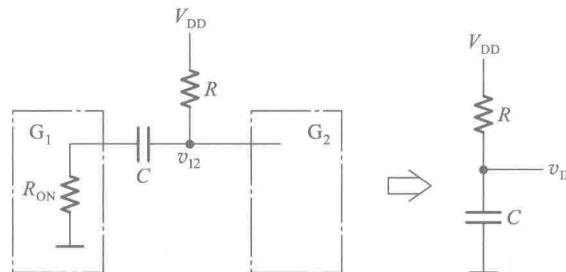

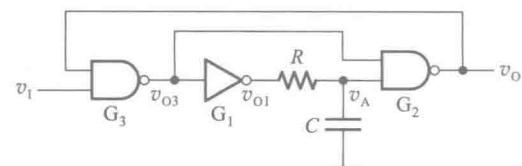

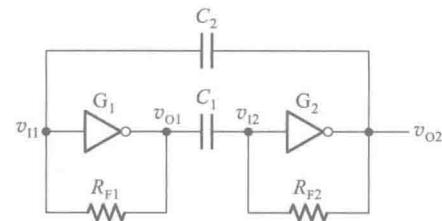

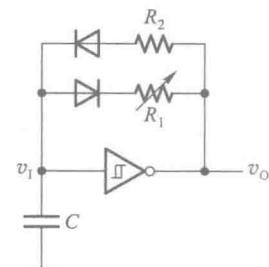

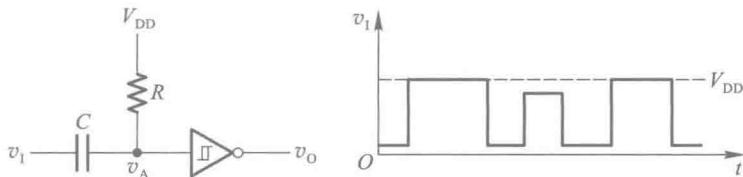

| 7.3.1 用门电路组成的单稳态电路.....                   | 357        |

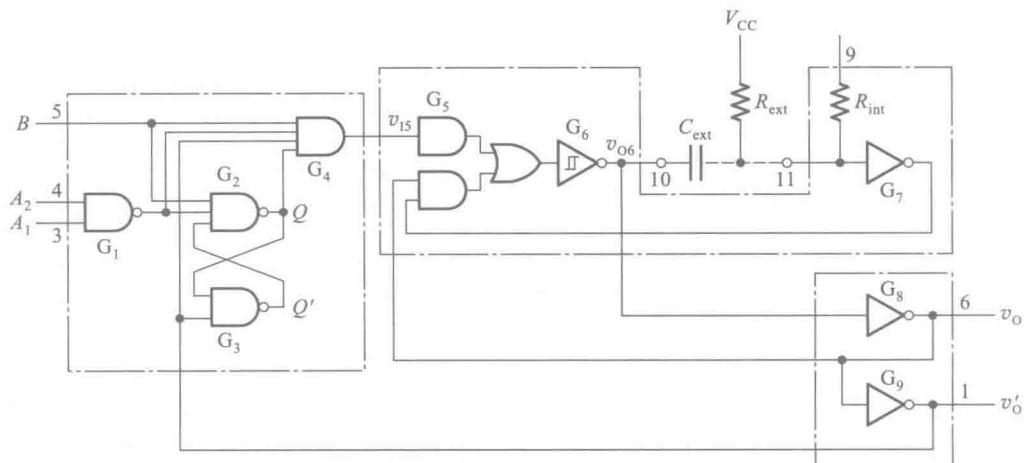

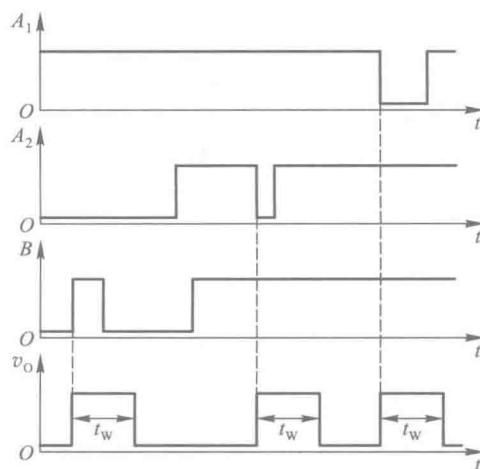

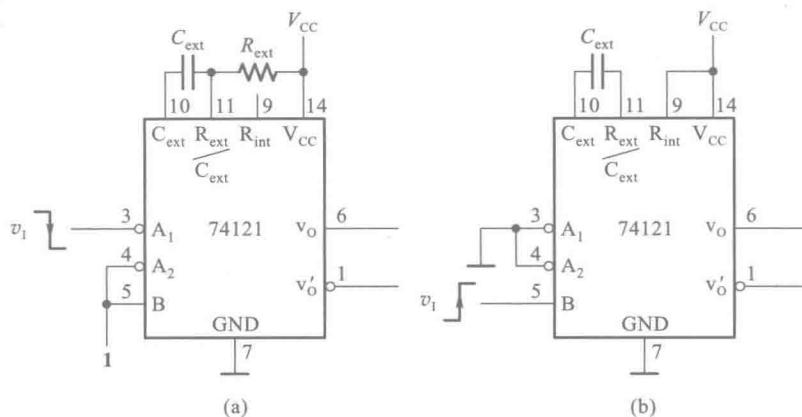

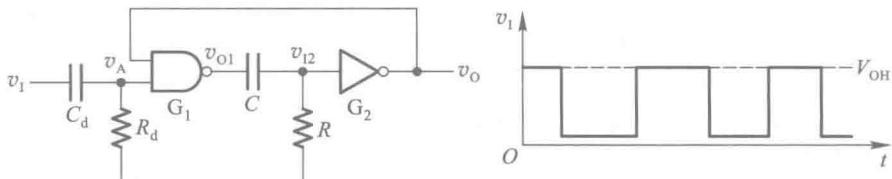

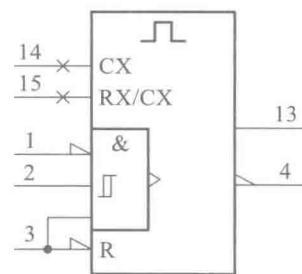

| 7.3.2 集成单稳态电路 .....                       | 361        |

|                                 |     |

|---------------------------------|-----|

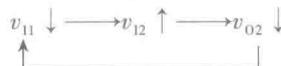

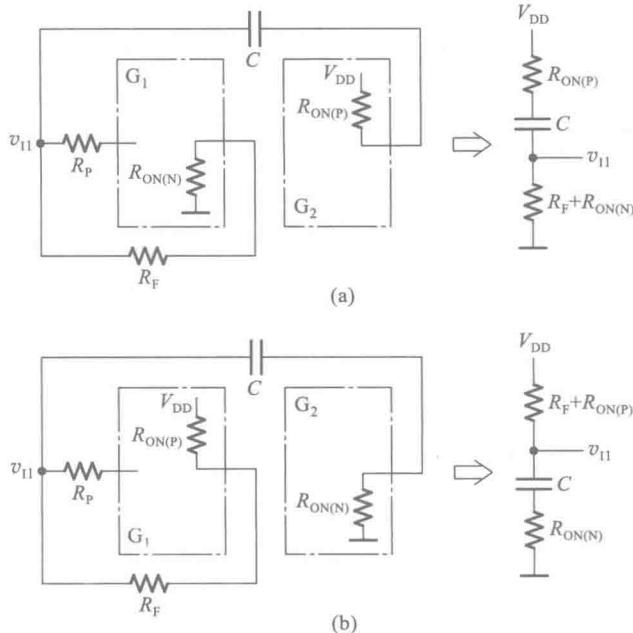

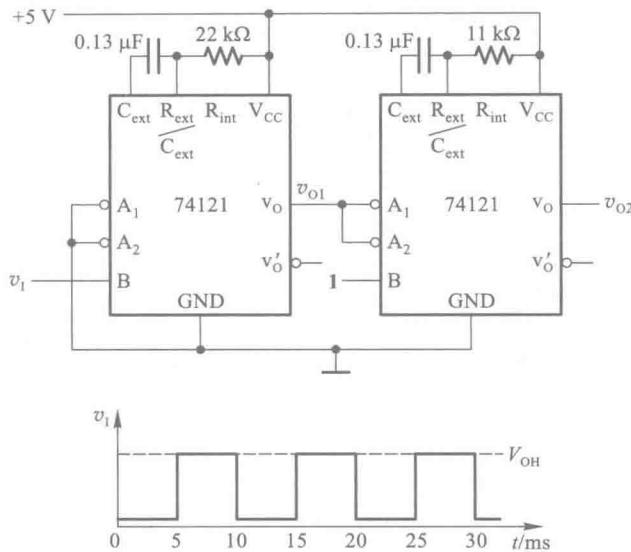

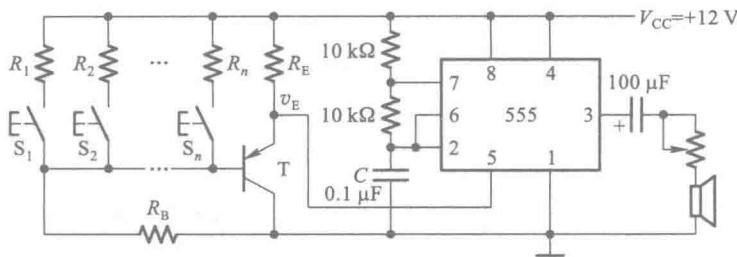

| 7.4 多谐振荡电路 .....                | 364 |

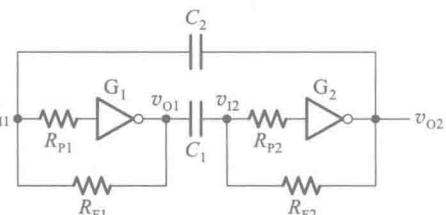

| 7.4.1 对称式多谐振荡电路 .....           | 364 |

| 7.4.2 非对称式多谐振荡电路 .....          | 367 |

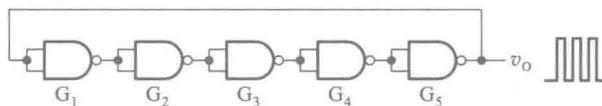

| 7.4.3 环形振荡电路 .....              | 370 |

| 7.4.4 用施密特触发电路构成的多谐振荡电路 .....   | 372 |

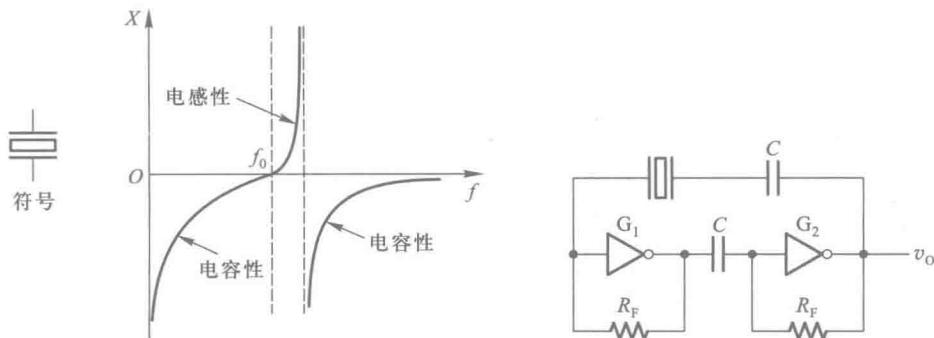

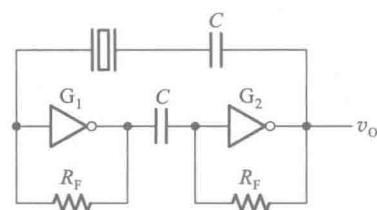

| 7.4.5 石英晶体多谐振荡电路 .....          | 374 |

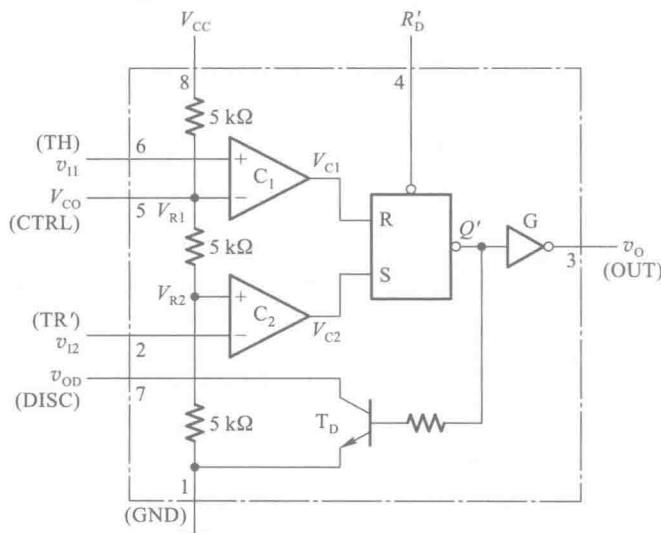

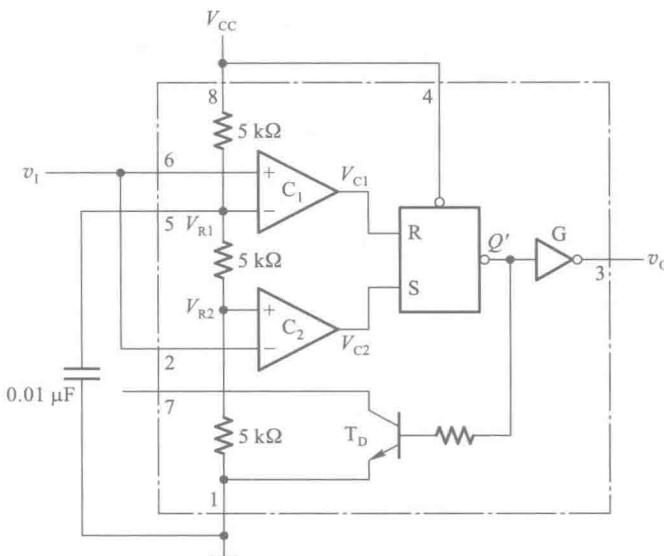

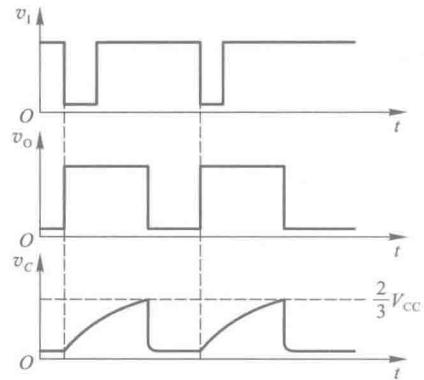

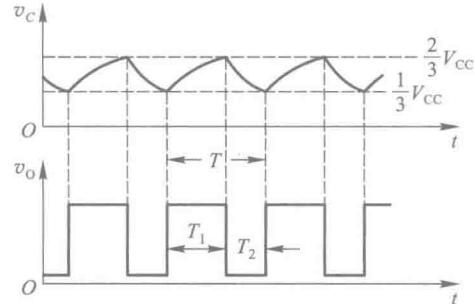

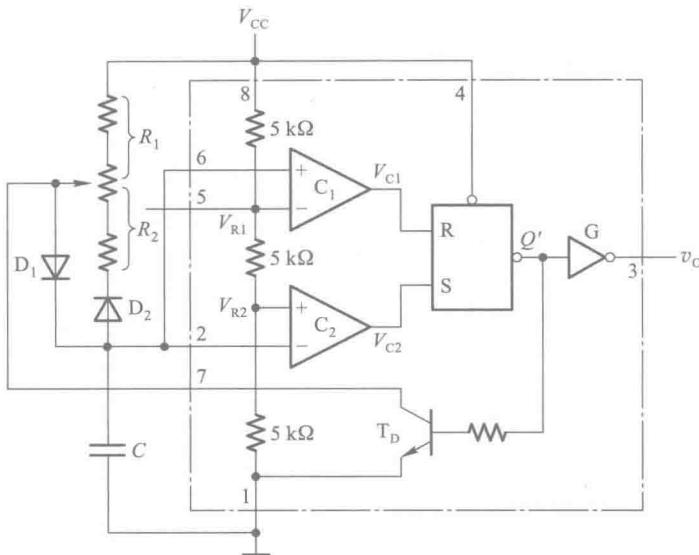

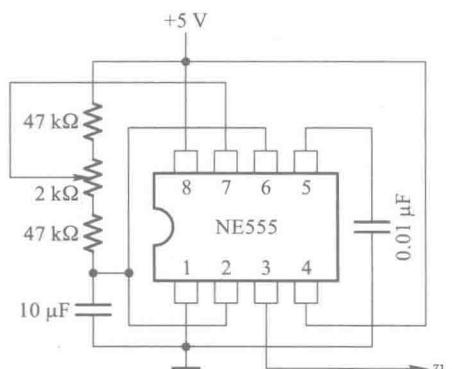

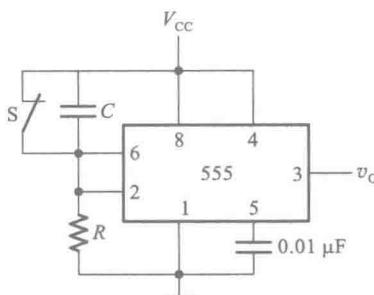

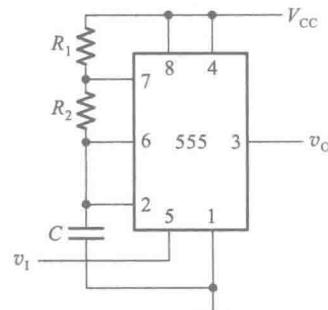

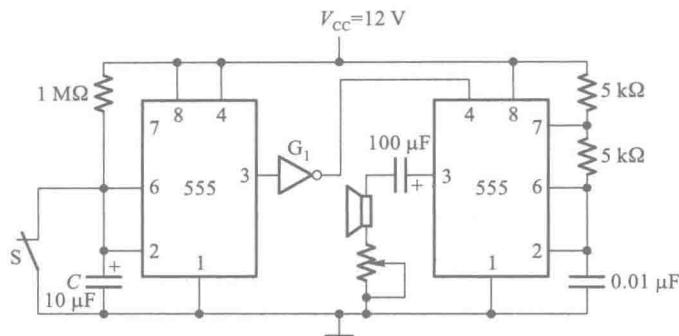

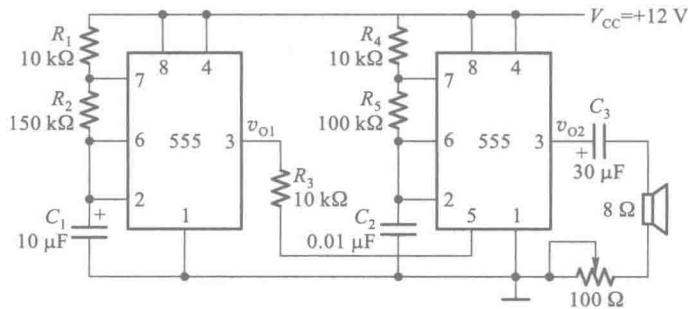

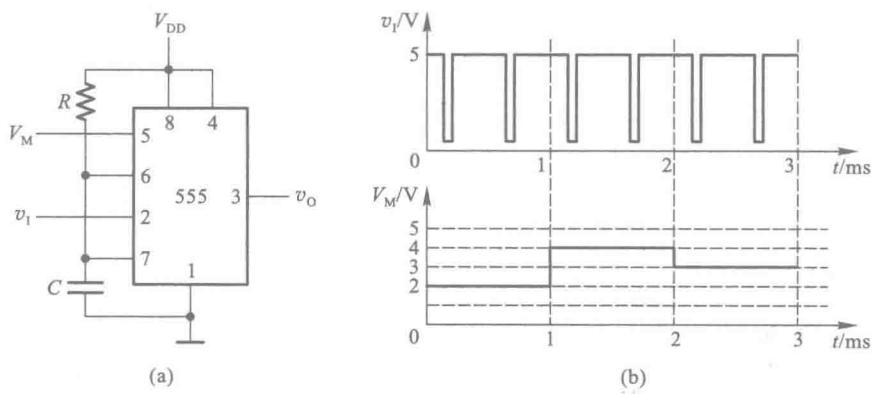

| 7.5 555 定时器及其应用 .....           | 375 |

| 7.5.1 555 定时器的电路结构和功能 .....     | 375 |

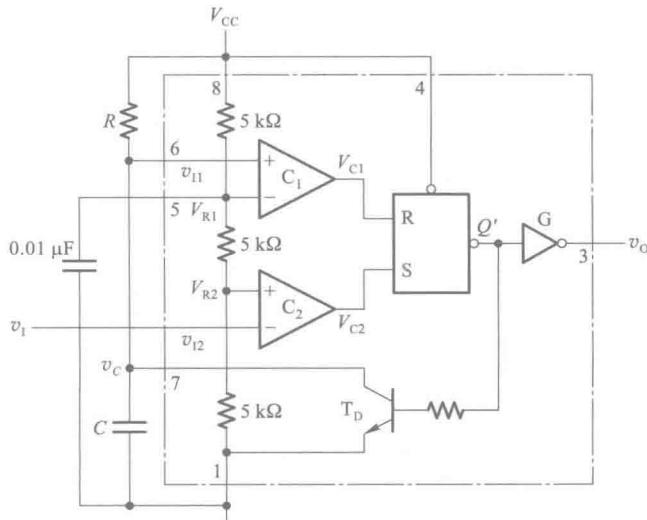

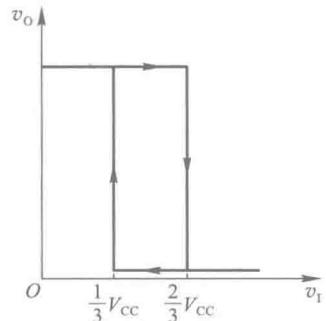

| 7.5.2 用 555 定时器接成的施密特触发电路 ..... | 377 |

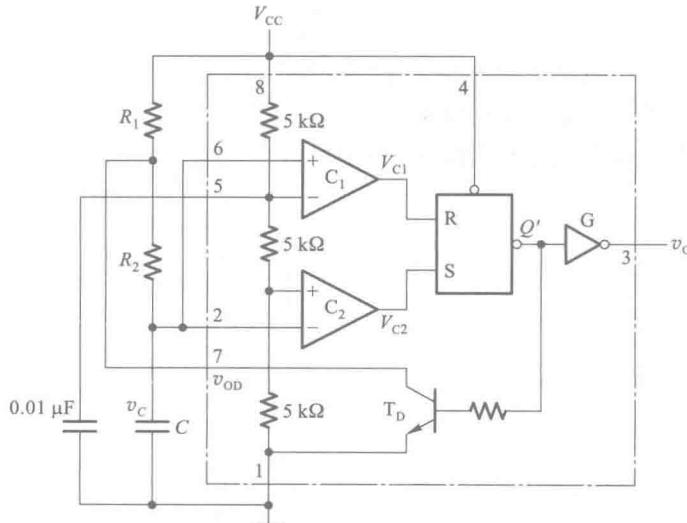

| 7.5.3 用 555 定时器接成的单稳态电路 .....   | 378 |

| 7.5.4 用 555 定时器接成的多谐振荡电路 .....  | 379 |

| 本章小结 .....                      | 382 |

| 习题 .....                        | 383 |

|                                           |     |

|-------------------------------------------|-----|

| <b>第八章 数-模和模-数转换</b> .....                | 388 |

| 8.1 概述 .....                              | 388 |

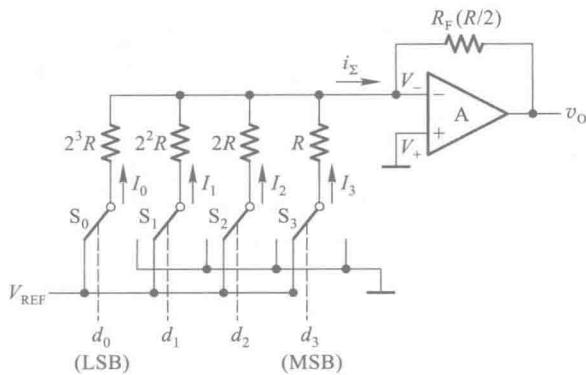

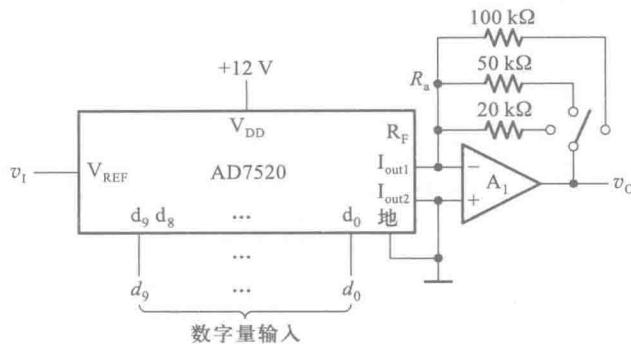

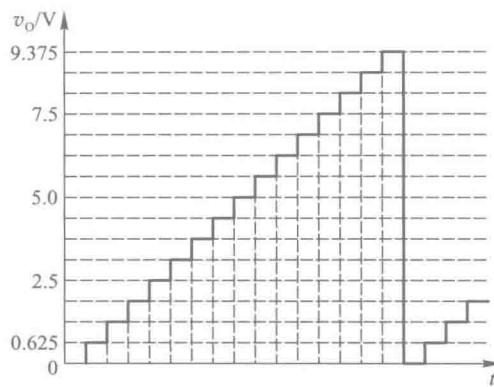

| 8.2 D/A 转换器的电路结构和工作原理 .....               | 389 |

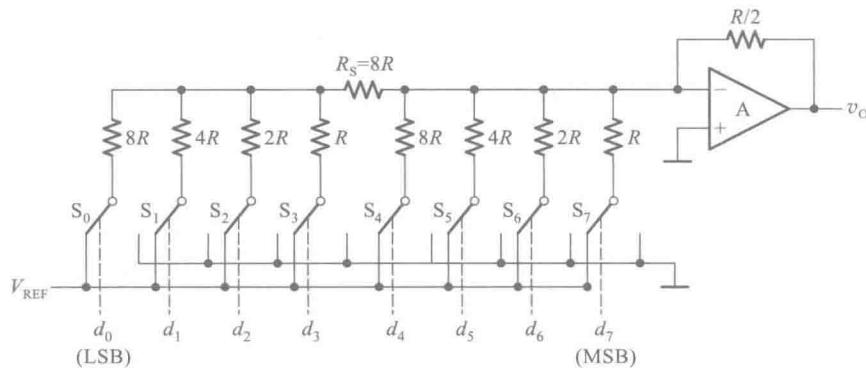

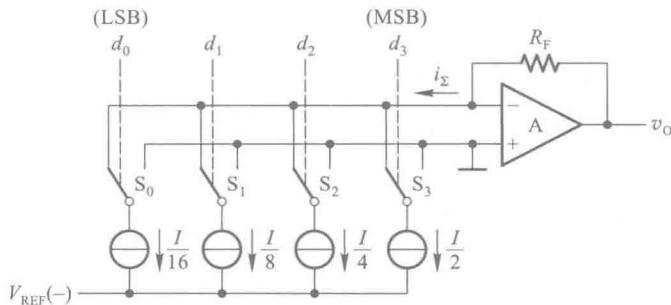

| 8.2.1 权电阻网络 D/A 转换器 .....                 | 389 |

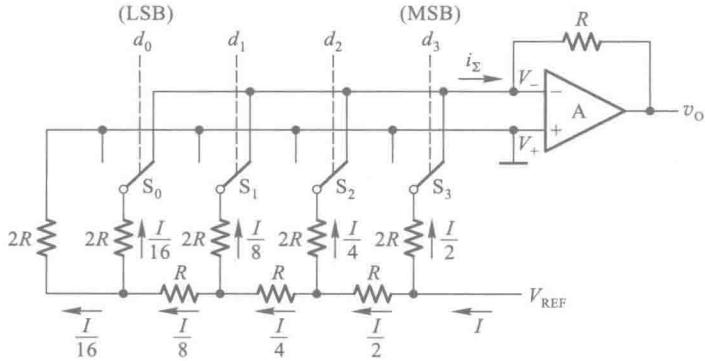

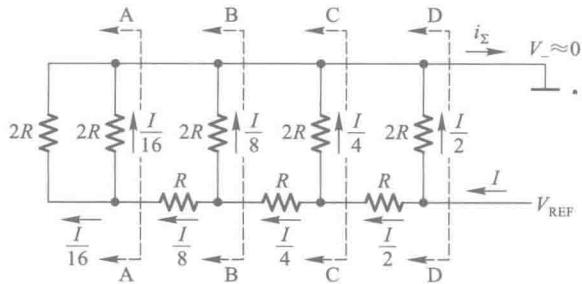

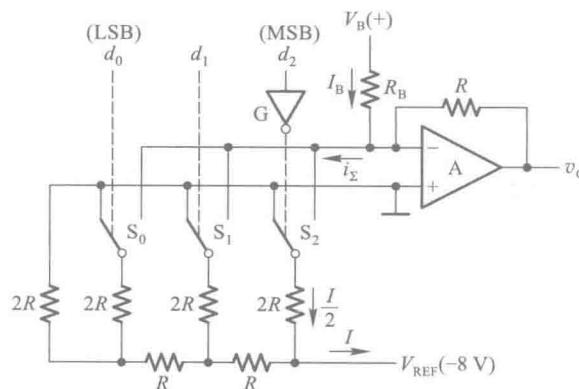

| 8.2.2 倒 T 形电阻网络 D/A 转换器 .....             | 391 |

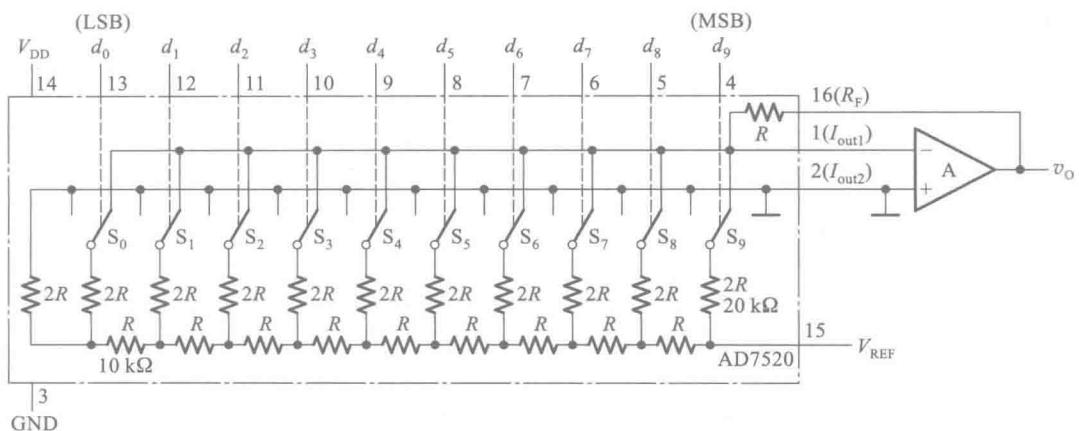

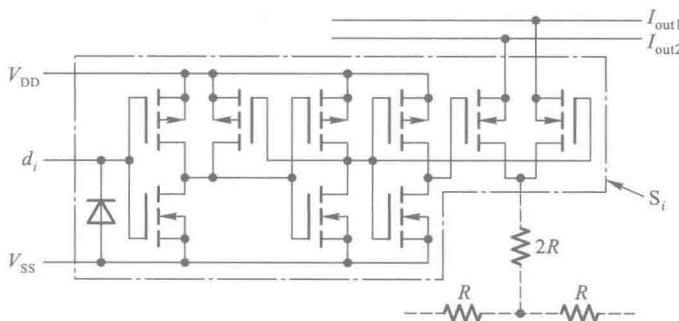

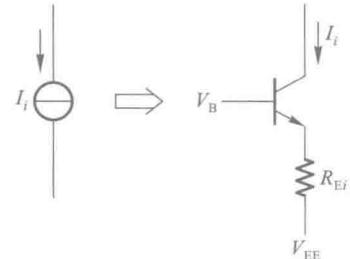

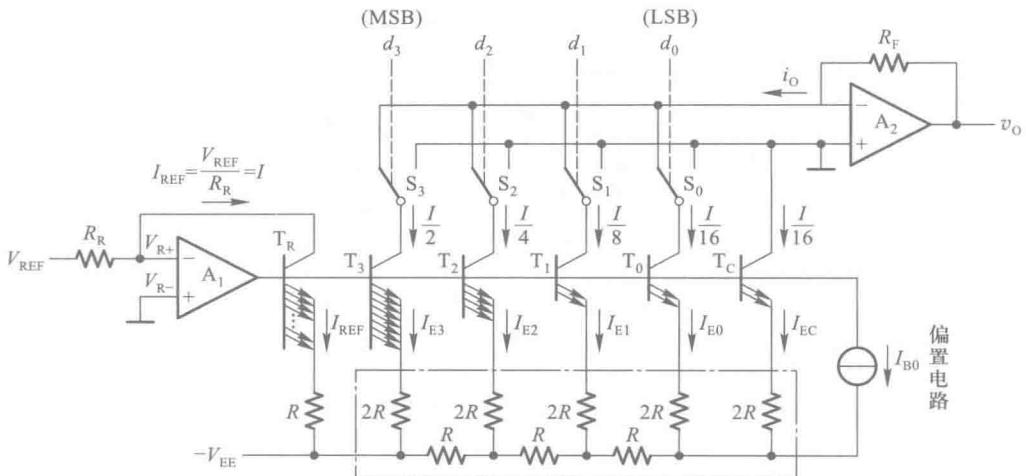

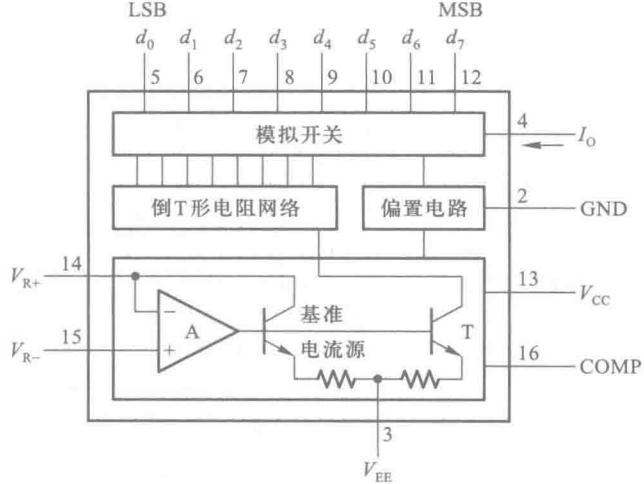

| 8.2.3 权电流型 D/A 转换器 .....                  | 393 |

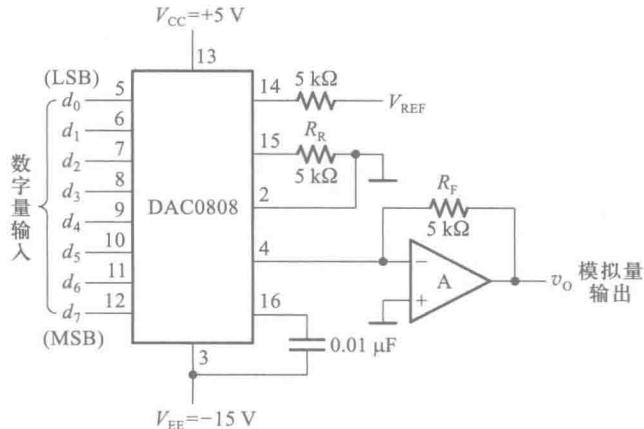

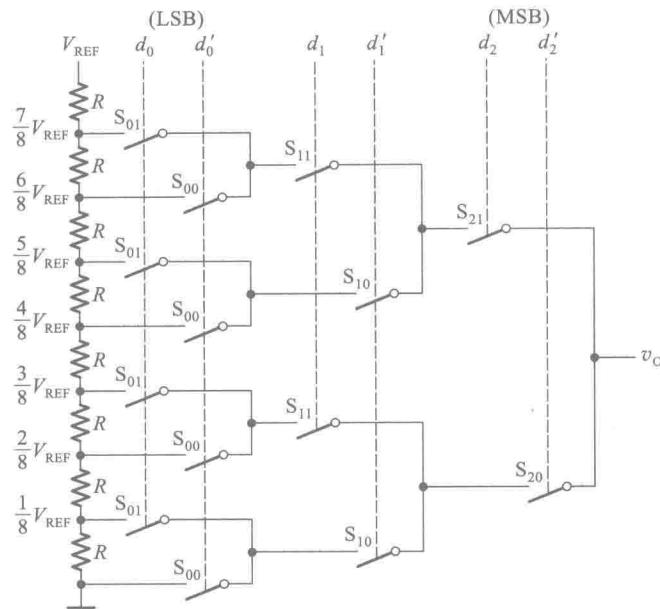

| * 8.2.4 开关树型 D/A 转换器 .....                | 396 |

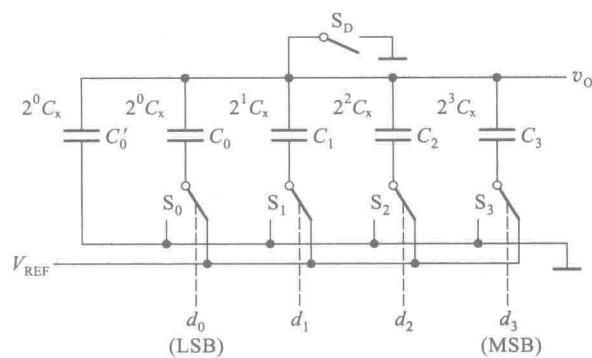

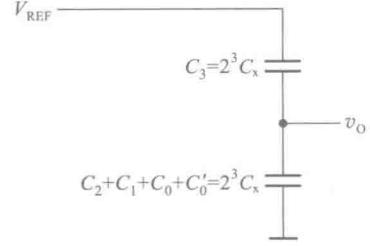

| * 8.2.5 权电容网络 D/A 转换器 .....               | 397 |

| 8.2.6 具有双极性输出的 D/A 转换器 .....              | 398 |

| 8.3 D/A 转换器的转换精度与转换速度 .....               | 400 |

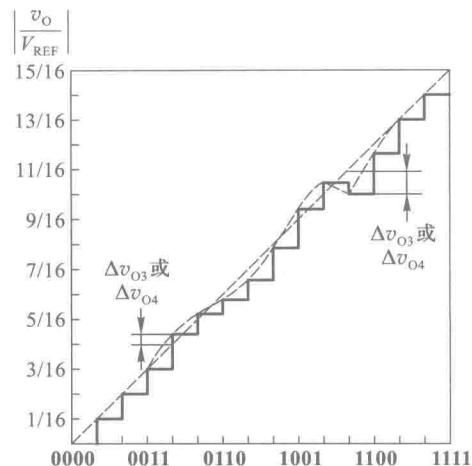

| 8.3.1 D/A 转换器的转换精度 .....                  | 400 |

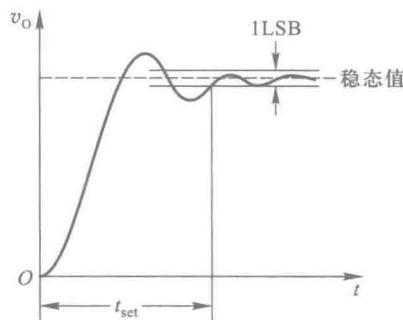

| 8.3.2 D/A 转换器的转换速度 .....                  | 404 |

| 8.4 A/D 转换的基本原理 .....                     | 404 |

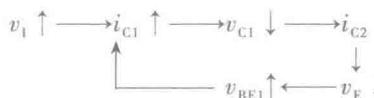

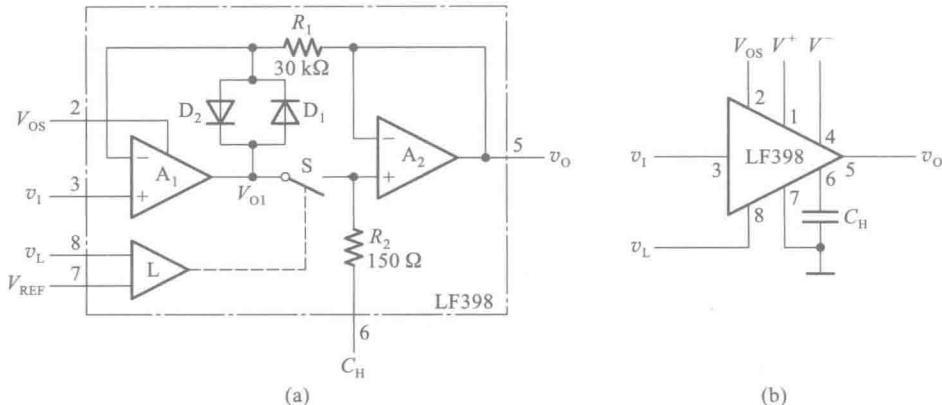

| 8.5 取样-保持电路 .....                         | 407 |

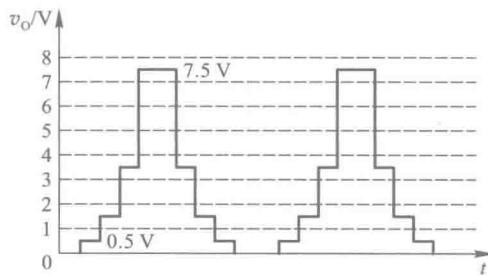

| 8.6 A/D 转换器的电路结构和工作原理 .....               | 408 |

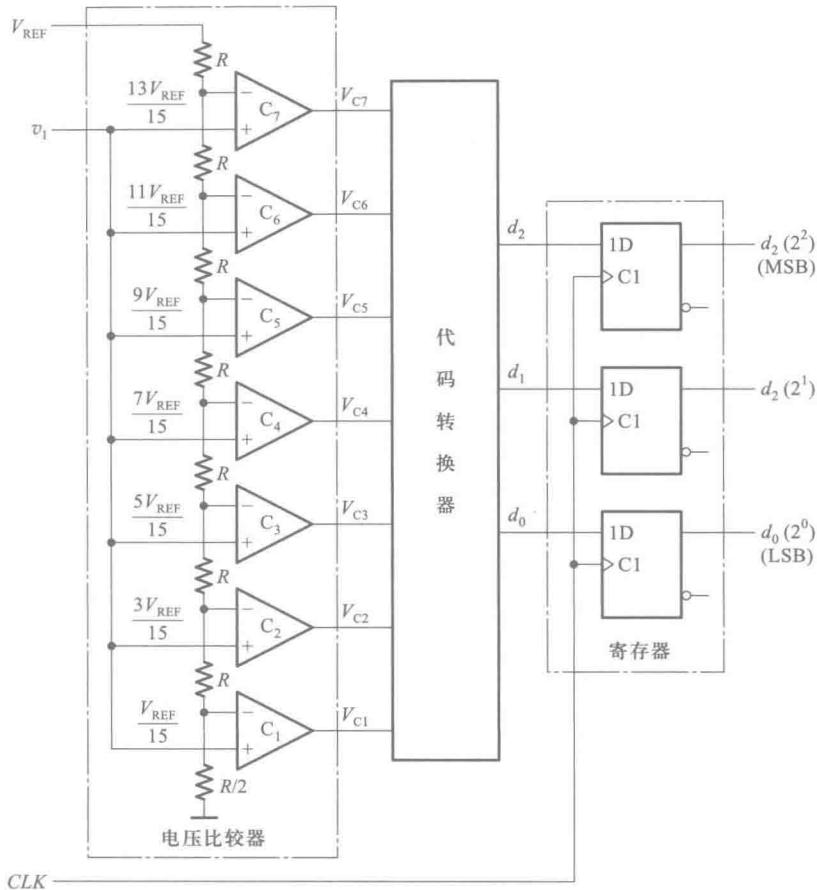

| 8.6.1 并联比较型 A/D 转换器 .....                 | 408 |

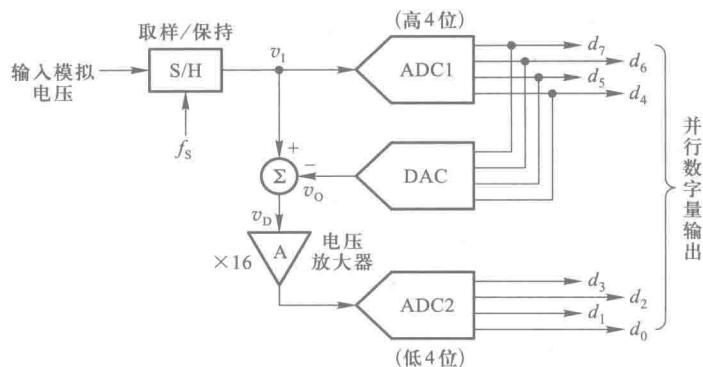

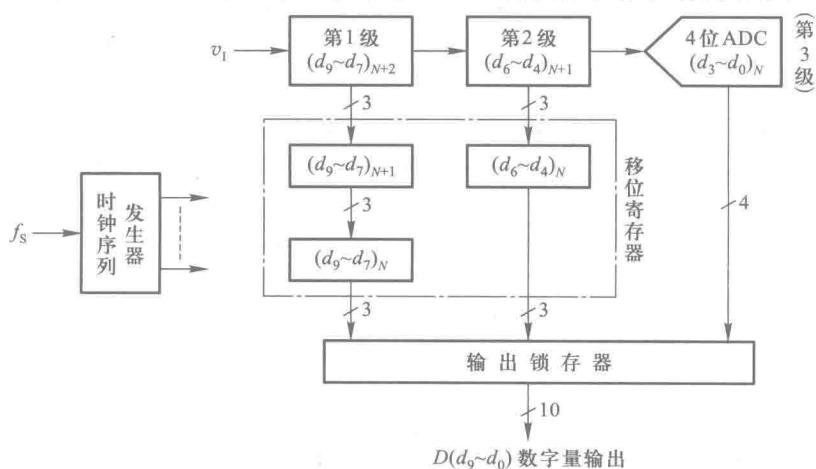

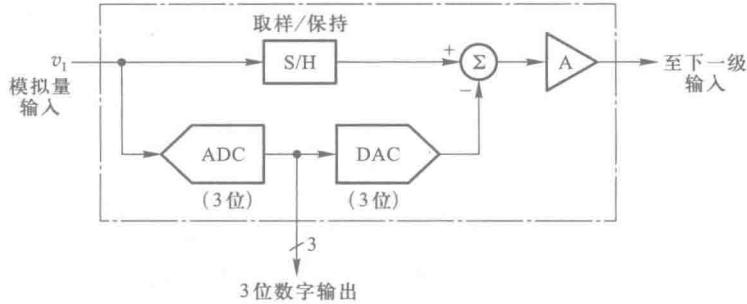

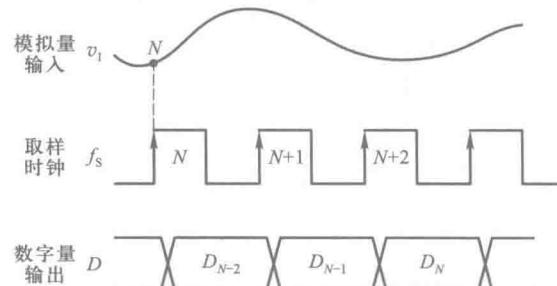

| * 8.6.2 流水线型 A/D 转换器 .....                | 411 |

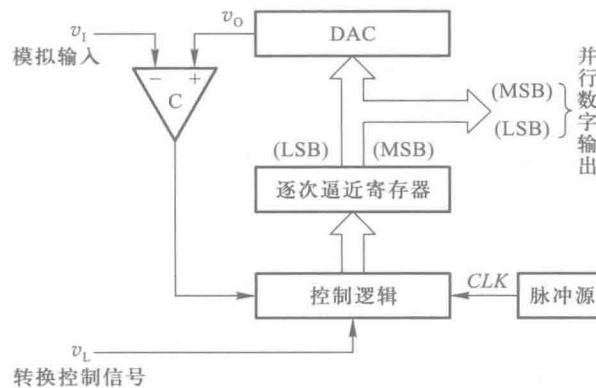

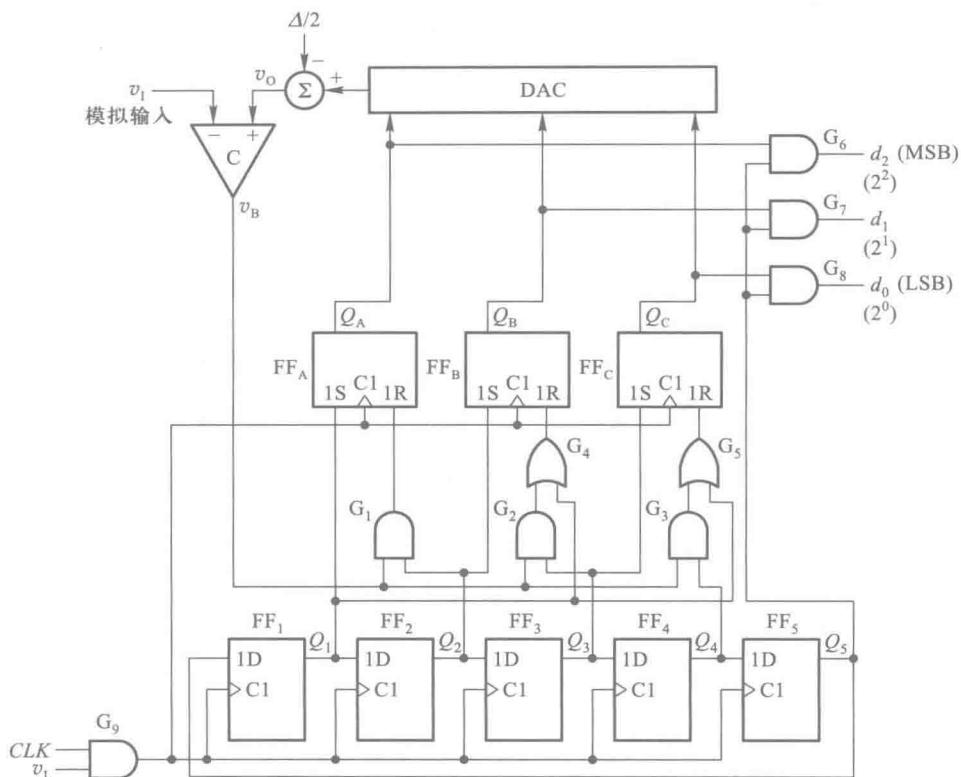

| 8.6.3 逐次逼近型 A/D 转换器 .....                 | 413 |

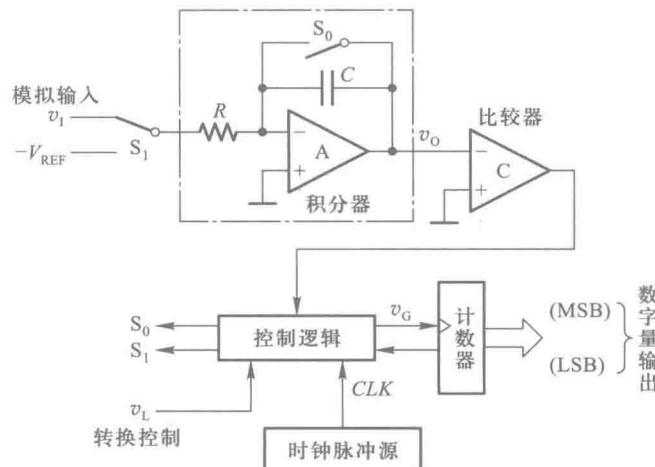

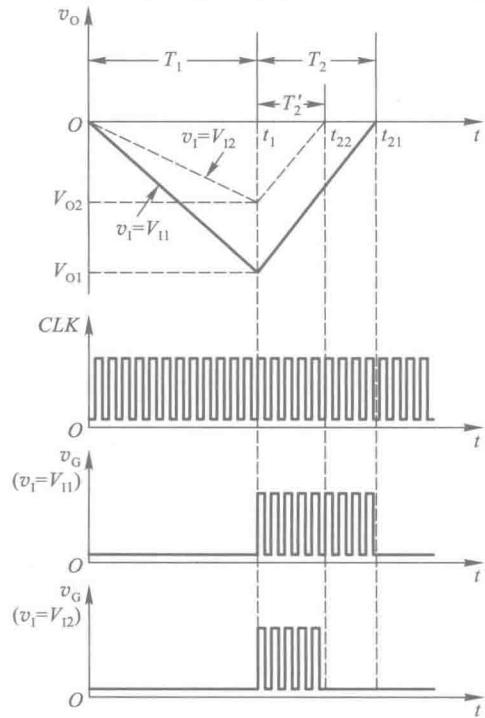

| 8.6.4 双积分型 A/D 转换器 .....                  | 415 |

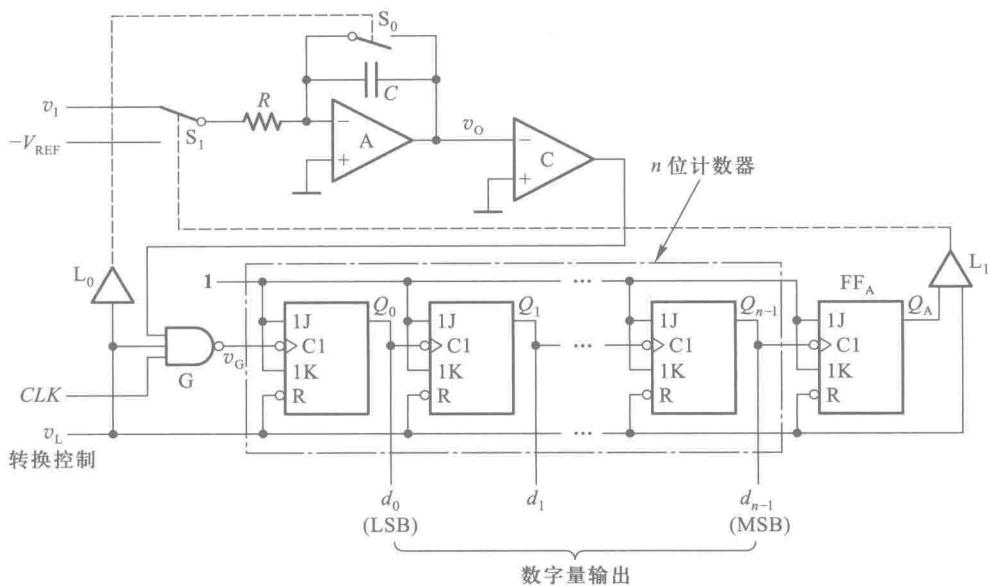

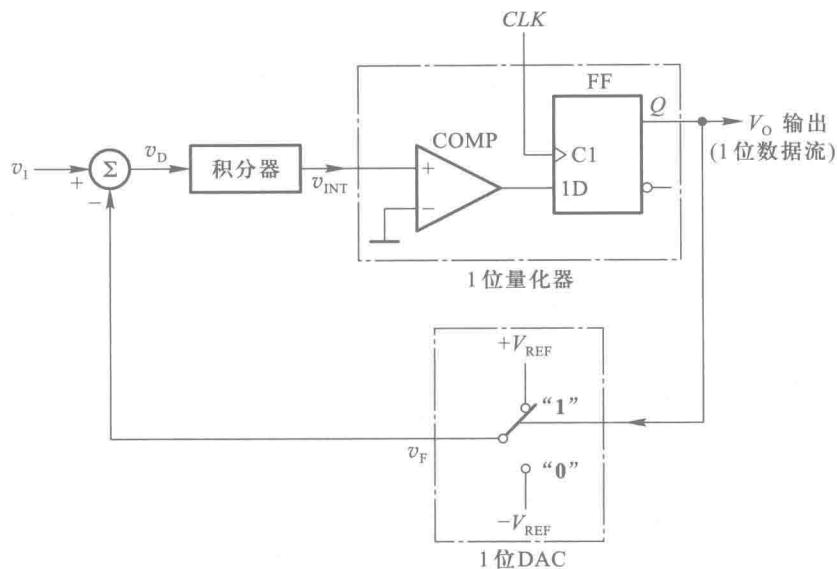

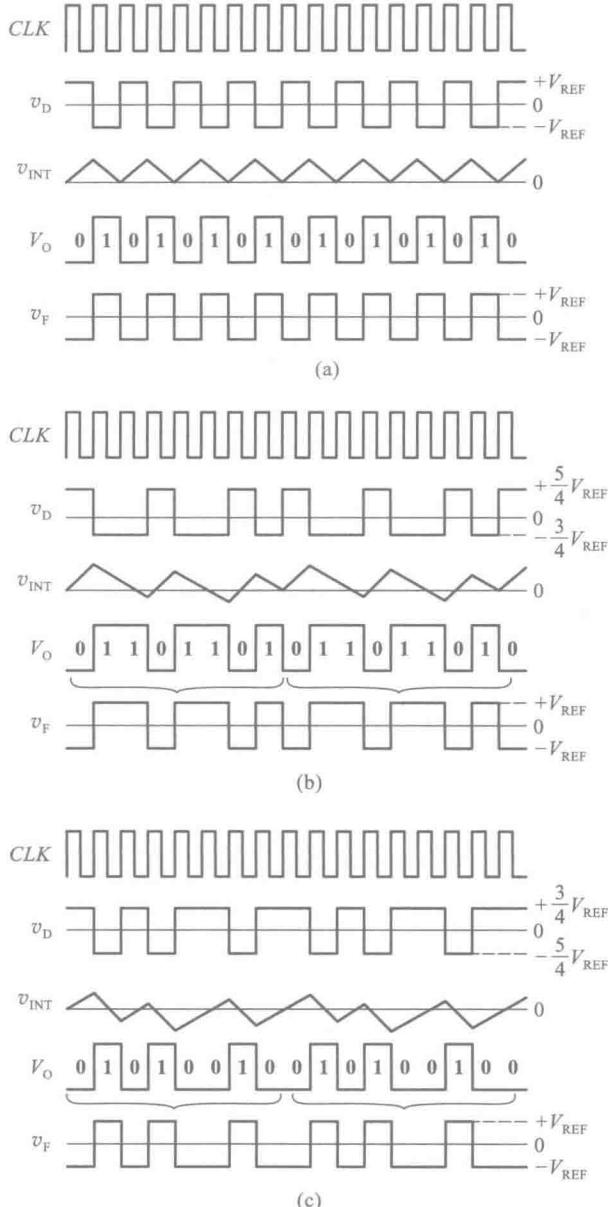

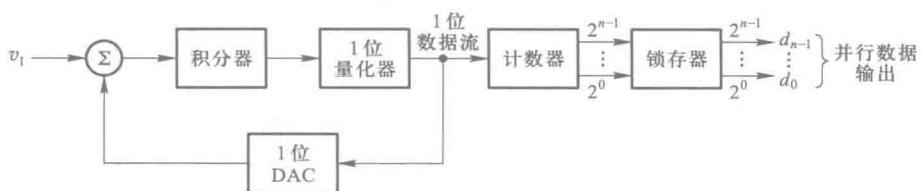

| * 8.6.5 $\Sigma - \Delta$ 型 A/D 转换器 ..... | 418 |

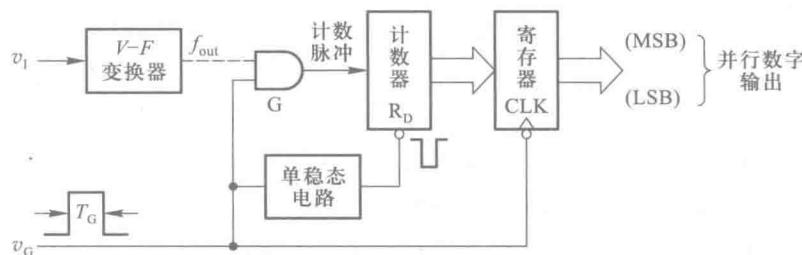

| 8.6.6 V-F 变换型 A/D 转换器 .....               | 421 |

| 8.7 A/D 转换器的转换精度与转换速度 .....               | 426 |

| 8.7.1 A/D 转换器的转换精度 .....                  | 426 |

| 8.7.2 A/D 转换器的转换速度 .....                  | 427 |

|                                                         |     |

|---------------------------------------------------------|-----|

| 本章小结 .....                                              | 428 |

| 习题 .....                                                | 429 |

| <br>                                                    |     |

| 附录一 可编程逻辑器件(PLD)分类 .....                                | 435 |

| <br>                                                    |     |

| 附录二 《电气简图用图形符号——二进制逻辑单元》<br>(GB/T 4728.12—2005)简介 ..... | 453 |

| <br>                                                    |     |

| 附录三 基本逻辑单元图形符号对照表 .....                                 | 462 |

| <br>                                                    |     |

| 部分习题答案 .....                                            | 464 |

| <br>                                                    |     |

| 参考文献 .....                                              | 478 |

| <br>                                                    |     |

| 名词索引 .....                                              | 479 |

# 绪论

---

电子技术是一门研究电子器件及其应用的学科,涉及的领域极其广阔。可以毫不夸张地说,时至今日,电子技术的应用已经渗透到了人类活动的一切领域。从电视、电话、移动通信、计算机、医疗仪器、现代的家用电器到各种先进的仪器设备,其中无不包含着电子技术的研究成果。

## 电子技术发展历程的简短回顾

从 1904 年第一只真空二极管问世算起,虽然已经过了一百余年,但是电子技术及其应用仍然充满着蓬勃发展的生机。回顾电子技术发展的历史不难发现,电子技术的发展和进步,是与电子器件的更新紧密相连的。电子器件是一种通过控制电子在其中的运动而工作的器件。20 世纪初期,首先得到应用的是真空电子管(简称真空管)。真空管的电极封装在一个真空的玻璃或金属外壳中,依靠将阴极加热产生电子流而进行工作。由于真空管的成功应用,带来了通讯技术的大发展,催生了无线电通讯、无线电广播和电视。

由于真空管工作时必须将阴极加热至很高的温度才能发射出电子流,所以不仅功耗大,而且寿命短,同时体积和重量也比较大。1947 年沃尔特·布兰坦(Walter Brattain)、约翰·巴丁(John Bardeen)和威廉·肖克利(William Shockley)发明了晶体管,也就是通常所说的半导体三极管。和电子管相比,晶体管不仅功耗小、寿命长,而且体积和重量也大大减小了。因此,晶体管在几乎所有电子技术应用领域中逐步取代了电子管,从而导致了电子设备大规模的更新换代。同时,也有力地扩展了电子技术的应用领域。用晶体管制作的电子计算机开始崭露头角,在越来越多的领域中得到了应用。发明晶体管的几位科学家由于这项发明而获得了诺贝尔奖。

虽然使用了晶体管以后电子设备的体积和重量更小了,但是仍然满足不了许多应用领域(例如移动通信设备、各种便携式设备、航空航天仪器和设备等)对电子电路微型化的需求。1958 年,杰克·科尔比(Jack Kilby)发明了集成电路。他将若干个晶体管、电阻和相互间的连接线成功地制作在一片很小的硅片上,成为“集成电路”,从而开辟了电子电路微型化的新途径。

随着微电子技术的不断进步,集成电路的集成度迅速提高。1965 年戈登·摩尔(Gordon E. Moore)在《Electronics》杂志上发表的一篇文章中提出,在未来的十年中,集成电路中晶体管的数目将以每年翻一番的速度迅速增长(20 世纪 80 年代末期以后,又将集成度翻番的时间放慢到了 18 个月),每个晶体管的价格也相应地降低为原来的一半。这一科学的预测已经为后来的实践所证明,并且被称作“摩尔定律”。到了 20 世纪 70 年代,大规模集成电路的集成度已经达到了每片数千万个晶体管。大规模集成电路的普及应用不仅又一次导致了电子设备大规模更新换代,而且极大地拓展了电子技术的应用领域。

今天我们可以将上亿个晶体管集成在一片邮票大小的半导体硅片上,组成十分复杂的电

子电路，甚至可以把过去的一台计算机制作在一片半导体硅片上，作成单片机，从而实现了计算机的微型化。我们还可以轻易地把一个复杂的电子系统集成在一个半导体硅片上，作成“片上系统”(System on Chip，简写成 SoC)，然后“植入”到各行各业的各种设备中，使这些设备的性能得到质的飞跃。如今集成电路不仅出现在各种电子仪器设备中，而且几乎无所不在。在科技发展的历史上，还从来没有任何一种技术能像微电子技术这样，对人类生产和生活产生如此广泛和深远的影响。因此，集成电路的发明者也当之无愧地获得了诺贝尔奖。

为了提高集成度，就必须缩小晶体管的尺寸，提高加工精度。到了 2010 年，集成电路的微细加工精度已经到达了 32 nm。由于集成度的提高最终将受到加工工艺极限的限制和晶体管物理极限的限制，因而摩尔定律也将失效。从 20 世纪 80 年代开始，各国的科学家已经开始探索制作集成度更高的、可以替代半导体集成电路的器件了。

### 数字电子电路和“数字化”浪潮

当我们仔细观察自然界中存在的各种物理量时不难发现，就其变化规律的特点而言，它们不外乎两大类。其中一类物理量的变化在时间上或数量上是连续的，我们把这一类物理量称为模拟量。例如加热炉里的温度，水库水位的高度，都属于这一类。

另外一类物理量的变化在时间上和数量上都是离散的。也就是说，它们的变化在时间上是不连续的，总是发生在一系列离散的瞬间。而且它们数值的大小和每次的增减变化都是某一个最小数量单位的整数倍。例如我们统计每天从装配线上输出的汽车数量，得到的就是一个数字量。

当我们把模拟量和数字量转换成电压(或电流)信号时，得到的电压(或电流)信号也分为模拟信号和数字信号两大类。工作在模拟信号下的电子电路称为模拟电子电路(简称模拟电路)，而工作在数字信号下的电子电路称为数字电子电路(简称数字电路)。

由于在数字电路中普遍采用的是二进制信号，每一位数字仅有 0 和 1 两个取值，所以只要电路能正确区分出两个不同状态就可以了，允许有一定的偏差。这就大大降低了对电路制造精度、工作条件以及运行环境的要求。而为了提高信号的精度，可以通过增加二进制数的位数来解决。相对而言，模拟电路在制造精度、工作条件和运行环境要求等方面比数字电路要严格得多。因此，首先制成的集成电路是数字集成电路。迄今为止，大多数的大规模和超大规模集成电路都属于数字集成电路。

自从数字集成电路问世以来，数字电路的应用得到了迅速的发展。尤其是在实现了计算机微型化以后，为了充分发挥数字电路在信号处理方面的强大优势，我们可以先将模拟信号按比例地转换成数字信号，然后送到数字电路(包括计算机)进行处理，最后再将处理结果根据需要转换成模拟信号输出。自 20 世纪 70 年代以来，这种用数字电路处理模拟信号的所谓“数字化”浪潮已经席卷了几乎所有的电子技术应用领域。

鉴于数字电路和模拟电路在基本概念、基本原理以及分析方法和设计方法上都有明显的不同，所以目前很多高等学校在教学计划中都分别设置了数字电子技术基础和模拟电子技术基础两门课程。本书是为数字电子技术基础课程编写的教材，只着重介绍有关数字电路的基本概念、基本原理、基本的分析方法和设计方法。同时，在讲解的过程中也介绍一些典型的应用电路。

### 可编程逻辑器件和 EDA 技术的应用

早期生产的数字集成电路逻辑功能都是固定不变的。要想改变它的逻辑功能,就必须改变内部各单元电路之间的连接,而这种连接在集成电路制作过程中已经固定下来了。虽然我们可以根据不同的功能需要设计和生产出相应的集成电路,但这种办法不仅成本高,而且设计和生产的周期很长。如果能够制作一种可以允许用户自行修改内部连接的集成电路,则只需要生产这种类型的通用集成电路,就能够满足不同用户的需要。于是可编程逻辑器件(Programmable Logic Device,简称 PLD)便应运而生。PLD 内部的电路结构可以通过写入编程数据来设置。不仅如此,有些 PLD 中写入的编程数据还可以擦除重写。PLD 最初出现在 20 世纪 60 年代的后期,80 年代以后有了迅猛的发展。现在已经可以把数千万个晶体管组成的、成百上千个各种类型的基本单元电路集成于一片 PLD 中。用这些基本单元电路足以组成一个十分复杂的数字系统,构成所谓的“片上系统”。目前 PLD 的应用已经相当普遍,特别是在新产品的研制和小批量产品的生产中,使用 PLD 的优势尤为明显。

显然,如此复杂的编程工作是无法用手工操作完成的。因此 PLD 的编程工作,包括编程数据的生成和写入,必须使用 EDA(Electronics Design Automation)技术方可完成。PLD 编程使用的 EDA 工具包含硬件和软件两部分。硬件部分由计算机和编程器组成。首先,必须将设计要求输入计算机。为此,开发了用于描述电路功能的硬件描述语言(Hardware Description Language,简称 HDL)和相应的编译程序。此外还必须有能够适应于选用器件的 PLD 的编程软件,以便完成编程数据的生成和写入。早期的 PLD 在编程时,需要先把计算机生成的编程数据输入编程器,然后再写入置于编程器上的 PLD 中。如今在大规模集成的 PLD 当中,越来越多地采用了“在系统可编程”(In System Programmable,简称 ISP)技术。这种器件在写入编程数据时,已经不需要使用编程器了,计算机生成的编程数据可以直接写入其中。而且,不需要将 PLD 从已经安装好的系统里取出,即可完成对它的编程操作。

从广义上讲,微处理器和单片机也是可编程的大规模数字集成电路。但是它们和 PLD 不同,对微处理器和单片机编程并不改变电路的内部连接结构,只是根据要求实现的功能写入相应的运行程序。这部分内容已超出本书讨论的范畴,在微型计算机原理等后续课程中会有全面而详细的介绍。

# 第一章

## 数制和码制

---

### 内容提要

本章首先介绍有关数制和码制的一些基本概念和术语,然后给出常用的数制和码制。此外,还将具体讲述不同数制之间的转换方法和二进制数算术运算的原理和方法。

### 1.1 概 述

数字电路所处理的各种数字信号都是以数码形式给出的。不同的数码既可以用来表示不同数量的大小,又可以用来表示不同的事物或事物的不同状态。

用数码表示数量的大小时,仅仅使用一位数码往往不够用,因而经常需要用进位计数制的方法组成多位数码使用。多位数码中每一位的构成方法和从低位到高位的进位规则称为数制。在绪论中我们曾经提及,数字电路中使用最多的数制是二进制,其次是在二进制基础上构成的十六进制和十进制。有时也用到八进制。

当两个数码分别表示两个数量大小时,可以进行数量间的加、减、乘、除等运算。这一类运算称为算术运算。鉴于目前数字电路中的算术运算最终都是以二进制运算进行的,所以在这一章里我们还将比较详细地讨论在数字电路中是采用什么方式完成二进制算术运算的。

在用不同数码表示不同事物或事物的不同状态时,这些数码已经不再具有表示数量大小的含义了,它们只是不同事物的代号而已。我们将这些数码称之为代码。例如在举行长跑比赛时,为便于识别运动员,通常要给每一位运动员编一个号码。显然,这些号码仅仅表示不同的运动员而已,没有数量大小的含义。

为了便于记忆和查找,在编制代码时总要遵循一定的规则,这些规则就称为码制。每个人都可以根据自己的需要选定编码规则,编制出一组代码。但是考虑到信息交换的需要,还必须制定一些大家共同使用的通用代码。例如目前国际上通用的美国信息交换标准代码(ASCII 码)就属于这一种。

### 1.2 几种常用的数制

#### 一、十进制

十进制是日常生活和工作中最常使用的进位计数制。在十进制数中,每一位有 0~9 十个数码,所以计数的基数是 10。超过 9 的数必须用多位数表示,其中低位和相邻高位之间的关系是

“逢十进一”，故称为十进制。例如

$$143.75 = 1 \times 10^2 + 4 \times 10^1 + 3 \times 10^0 + 7 \times 10^{-1} + 5 \times 10^{-2}$$

所以任意一个多位的十进制数  $D$  均可展开为

$$D = \sum k_i \times 10^i \quad (1.2.1)$$

式中  $k_i$  是第  $i$  位的系数，它可以是 0~9 这十个数码中的任何一个。若整数部分的位数是  $n$ ，小数部分的位数为  $m$ ，则  $i$  包含从  $n-1$  到 0 的所有正整数和从 -1 到  $-m$  的所有负整数，整数部分的最高位为  $n-1$ ，最低位为 0；小数部分的最高位为 -1，最低位为  $-m$ 。

若以  $N$  取代式(1.2.1)中的 10，即可得到多位任意进制( $N$  进制)数展开式的普遍形式

$$D = \sum k_i N^i \quad (1.2.2)$$

式中  $i$  的取值与式(1.2.1)的规定相同。 $N$  称为计数的基数， $k_i$  为第  $i$  位的系数， $N^i$  称为第  $i$  位的权。

## 二、二进制

目前在数字电路中应用最广泛的是二进制。在二进制数中，每一位仅有 0 和 1 两个可能的数码，所以计数基数为 2。低位和相邻高位间的进位关系是“逢二进一”，故称为二进制。

根据式(1.2.2)，任何一个二进制数均可展开为

$$D = \sum k_i 2^i \quad (1.2.3)$$

并可用上式计算出它所表示的十进制数的大小。例如

$$\begin{aligned} (101.11)_2 &= 1 \times 2^2 + 0 \times 2^1 + 1 \times 2^0 + 1 \times 2^{-1} + 1 \times 2^{-2} \\ &= (5.75)_{10} \end{aligned}$$

上式中分别使用下脚注 2 和 10 表示括号里的数是二进制数和十进制数。有时也用 B(Binary) 和 D(Decimal) 代替 2 和 10 这两个脚注。

## 三、八进制

在某些场合有时也使用八进制。八进制数的每一位有 0~7 八个不同的数码，计数的基数为 8。低位和相邻的高位之间的进位关系是“逢八进一”。任意一个八进制数可以展开为

$$D = \sum k_i 8^i \quad (1.2.4)$$

并可利用上式计算出与之等效的十进制数值。例如

$$\begin{aligned} (12.4)_8 &= 1 \times 8^1 + 2 \times 8^0 + 4 \times 8^{-1} \\ &= (10.5)_{10} \end{aligned}$$

有时也用 O(Octal) 代替下脚注 8，表示八进制数。

## 四、十六进制

十六进制数的每一位有十六个不同的数码，分别用 0~9、A(10)、B(11)、C(12)、D(13)、E(14)、F(15) 表示。因此，任意一个十六进制数均可展开为

$$D = \sum k_i 16^i \quad (1.2.5)$$

并可由此式计算出它所表示的十进制数值。例如

$$\begin{aligned} (2A.7F)_{16} &= 2 \times 16^1 + 10 \times 16^0 + 7 \times 16^{-1} + 15 \times 16^{-2} \\ &= (42.496\ 093\ 7)_{10} \end{aligned}$$

式中的下脚注 16 表示括号里的数是十六进制数，有时也用 H(Hexadecimal)代替这个脚注。

由于目前在微型计算机中普遍采用 8 位、16 位和 32 位二进制并行运算，而 8 位、16 位和 32 位的二进制数可以用 2 位、4 位和 8 位的十六进制数表示，因而用十六进制符号书写程序十分简便。

表 1.2.1 是十进制数 0~15 与等值二进制、八进制、十六进制数的对照表。

表 1.2.1 不同进制数的对照表

| 十进制( Decimal ) | 二进制( Binary ) | 八进制( Octal ) | 十六进制( Hexadecimal ) |

|----------------|---------------|--------------|---------------------|

| 00             | <b>0000</b>   | 00           | 0                   |

| 01             | <b>0001</b>   | 01           | 1                   |

| 02             | <b>0010</b>   | 02           | 2                   |

| 03             | <b>0011</b>   | 03           | 3                   |

| 04             | <b>0100</b>   | 04           | 4                   |

| 05             | <b>0101</b>   | 05           | 5                   |

| 06             | <b>0110</b>   | 06           | 6                   |

| 07             | <b>0111</b>   | 07           | 7                   |

| 08             | <b>1000</b>   | 10           | 8                   |

| 09             | <b>1001</b>   | 11           | 9                   |

| 10             | <b>1010</b>   | 12           | A                   |

| 11             | <b>1011</b>   | 13           | B                   |

| 12             | <b>1100</b>   | 14           | C                   |

| 13             | <b>1101</b>   | 15           | D                   |

| 14             | <b>1110</b>   | 16           | E                   |

| 15             | <b>1111</b>   | 17           | F                   |

### 复习思考题

R1.2.1 写出 4 位二进制数、4 位八进制数和 4 位十六进制数的最大数。

R1.2.2 与 4 位二进制数、4 位八进制数、4 位十六进制数的最大值等值的十进制数各为多少？

## 1.3 不同数制间的转换

### 一、二-十转换

将二进制数转换为等值的十进制数称为二-十转换。转换时只要将二进制数按式(1.2.3)

展开,然后将所有各项的数值按十进制数相加,就可以得到等值的十进制数了。例如

$$\begin{aligned} (1011.01)_2 &= 1 \times 2^3 + 0 \times 2^2 + 1 \times 2^1 + 1 \times 2^0 + 0 \times 2^{-1} + 1 \times 2^{-2} \\ &= (11.25)_{10} \end{aligned}$$

## 二、十-二转换

所谓十-二转换,就是将十进制数转换为等值的二进制数。

首先讨论整数的转换。

假定十进制整数为  $(S)_{10}$ ,等值的二进制数为  $(k_n k_{n-1} \dots k_0)_2$ ,则依式(1.2.3)可知

$$\begin{aligned} (S)_{10} &= (k_n 2^n + k_{n-1} 2^{n-1} + \dots + k_1 2^1 + k_0 2^0)_2 \\ &= 2(k_n 2^{n-1} + k_{n-1} 2^{n-2} + \dots + k_1)_2 + k_0 \end{aligned} \quad (1.3.1)$$

上式表明,若将  $(S)_{10}$ 除以 2,则得到的商为  $k_n 2^{n-1} + k_{n-1} 2^{n-2} + \dots + k_1$ ,而余数即  $k_0$ 。

同理,可将式(1.3.1)除以 2 得到的商写成

$$(k_n 2^{n-1} + k_{n-1} 2^{n-2} + \dots + k_1)_2 = 2(k_n 2^{n-2} + k_{n-1} 2^{n-3} + \dots + k_2)_2 + k_1 \quad (1.3.2)$$

由式(1.3.2)不难看出,若将  $(S)_{10}$ 除以 2 所得的商再次除以 2,则所得余数即  $k_1$ 。

依此类推,反复将每次得到的商再除以 2,就可求得二进制数的每一位了。

例如,将  $(173)_{10}$ 化为二进制数可如下进行

$$\begin{array}{r} 2 | 173 & \dots \text{余数 } = 1 = k_0 \\ 2 | 86 & \dots \text{余数 } = 0 = k_1 \\ 2 | 43 & \dots \text{余数 } = 1 = k_2 \\ 2 | 21 & \dots \text{余数 } = 1 = k_3 \\ 2 | 10 & \dots \text{余数 } = 0 = k_4 \\ 2 | 5 & \dots \text{余数 } = 1 = k_5 \\ 2 | 2 & \dots \text{余数 } = 0 = k_6 \\ 2 | 1 & \dots \text{余数 } = 1 = k_7 \\ 0 \end{array}$$

故  $(173)_{10} = (10101101)_2$ 。

其次讨论小数的转换。

若  $(S)_{10}$ 是一个十进制的小数,对应的二进制小数为  $(0.k_{-1} k_{-2} \dots k_{-m})_2$ ,则据式(1.2.3)可知

$$(S)_{10} = (k_{-1} 2^{-1} + k_{-2} 2^{-2} + \dots + k_{-m} 2^{-m})_2$$

将上式两边同乘以 2 得到

$$2(S)_{10} = k_{-1} + (k_{-2} 2^{-1} + k_{-3} 2^{-2} + \dots + k_{-m} 2^{-m+1})_2 \quad (1.3.3)$$

式(1.3.3)说明,将小数  $(S)_{10}$ 乘以 2 所得乘积的整数部分即  $k_{-1}$ 。

同理,将乘积的小数部分再乘以 2 又可得到

$$2(k_{-2} 2^{-1} + k_{-3} 2^{-2} + \dots + k_{-m} 2^{-m+1})_2 = k_{-2} + (k_{-3} 2^{-1} + \dots + k_{-m} 2^{-m+2})_2 \quad (1.3.4)$$

亦即乘积的整数部分就是  $k_{-2}$ 。

依此类推,将每次乘 2 后所得乘积的小数部分再乘以 2,便可求出二进制小数的每一位了。

例如,将  $(0.8125)_{10}$ 化为二进制小数时可如下进行

$$\begin{array}{r}

0.8125 \\

\times \quad \quad 2 \\

\hline

1.6250 \quad \text{整数部分} = 1 = k_{-1}

\end{array}$$

$$\begin{array}{r}

0.6250 \\

\times \quad \quad 2 \\

\hline

1.2500 \quad \text{整数部分} = 1 = k_{-2}

\end{array}$$

$$\begin{array}{r}

0.2500 \\

\times \quad \quad 2 \\

\hline

0.5000 \quad \text{整数部分} = 0 = k_{-3}

\end{array}$$

$$\begin{array}{r}

0.5000 \\

\times \quad \quad 2 \\

\hline

1.0000 \quad \text{整数部分} = 1 = k_{-4}

\end{array}$$

故  $(0.8125)_{10} = (0.1101)_2$ 。

### 三、二-十六转换

将二进制数转换为等值的十六进制数称为二-十六转换。

由于 4 位二进制数恰好有 16 个状态,而把这 4 位二进制数看作一个整体时,它的进位输出又正好是逢十六进一,所以只要从低位到高位将整数部分每 4 位二进制数分为一组并代之以等值的十六进制数,同时从高位到低位将小数部分的每 4 位数分为一组并代之以等值的十六进制数,即可得到对应的十六进制数。

例如,将  $(01011110.10110010)_2$  化为十六进制数时可得

$$\begin{array}{c}

(0101 \quad 1110. \quad 1011 \quad 0010)_2 \\

\downarrow \quad \downarrow \quad \downarrow \quad \downarrow \\

=(5 \quad E. \quad B \quad 2)_{16}

\end{array}$$

若二进制数整数部分最高一组不足 4 位时,用 0 补足 4 位;小数部分最低一组不足 4 位时,也需用 0 补足 4 位。

### 四、十六-二转换

十六-二转换是指将十六进制数转换为等值的二进制数。转换时只需将十六进制数的每一位用等值的 4 位二进制数代替就行了。

例如,将  $(8FA.C6)_{16}$  化为二进制数时得到

$$\begin{array}{c}

(8 \quad F \quad A. \quad C \quad 6)_{16} \\

\downarrow \quad \downarrow \quad \downarrow \quad \downarrow \quad \downarrow \\

=(1000 \quad 1111 \quad 1010. \quad 1100 \quad 0110)_2

\end{array}$$

### 五、八进制数与二进制数的转换

将二进制数转换为八进制数的二-八转换和将八进制数转换为二进制数的八-二转换,在方

法上与二-十六转换和十六-二转换的方法基本相同。

在将二进制数转换为八进制数时,只要将二进制数的整数部分从低位到高位每3位分为一组并代之以等值的八进制数,同时将小数部分从高位到低位每3位分为一组并代之以等值的八进制数就可以了。二进制数最高一组不足3位或小数部分最低一组不足3位时,仍需以0补足3位。

例如,若将 $(011110.010111)_2$ 化为八进制数,则得到

$$\begin{array}{cccc} (011 & 110. & 010 & 111)_2 \\ \downarrow & \downarrow & \downarrow & \downarrow \\ (3 & 6. & 2 & 7)_8 \end{array}$$

反之,若将八进制数转换为二进制数,则只要将八进制数的每一位代之以等值的3位二进制数即可。例如,将 $(52.43)_8$ 转换为二进制数时,得到

$$\begin{array}{cccc} (5 & 2. & 4 & 3)_8 \\ \downarrow & \downarrow & \downarrow & \downarrow \\ (101 & 010. & 100 & 011)_2 \end{array}$$

## 六、十六进制数与十进制数的转换

在将十六进制数转换为十进制数时,可根据式(1.2.5)将各位按权展开后相加求得。在将十进制数转换为十六进制数时,可以先转换为二进制数,然后再将得到的二进制数转换为等值的十六进制数。这两种转换方法上面已经讲过了。

### 复习思考题

R1.3.1 在十-二转换中,整数部分的转换方法和小数部分的转换方法有何不同?

R1.3.2 怎样将八进制数转换为十六进制数和将十六进制数转换为八进制数?

R1.3.3 怎样才能将十进制数转换为八进制数?

## 1.4 二进制算术运算

### 1.4.1 二进制算术运算的特点

当两个二进制数码表示两个数量大小时,它们之间可以进行数值运算,这种运算称为算术运算。二进制算术运算和十进制算术运算的规则基本相同,唯一的区别在于二进制数是“逢二进一”而不是十进制数的“逢十进一”。

例如,两个二进制数1001和0101的算术运算有

加法运算

$$\begin{array}{r}

1001 \\

+ 0101 \\

\hline

1110

\end{array}$$

减法运算

$$\begin{array}{r}

1001 \\

- 0101 \\

\hline

0100

\end{array}$$

乘法运算

$$\begin{array}{r}

1001 \\

\times 0101 \\

\hline

1001 \\

0000 \\

1001 \\

0000 \\

\hline

0101101

\end{array}$$

除法运算

$$\begin{array}{r}

1.11\cdots \\

0101 \overline{)1001} \\

0101 \\

\hline

1000 \\

0101 \\

\hline

0110 \\

0101 \\

\hline

0010

\end{array}$$

从上面的例子中可以看到二进制算术运算的两个特点,即二进制数的乘法运算可以通过若干次的“被乘数(或零)左移1位”和“被乘数(或零)与部分积相加”这两种操作完成;而二进制数的除法运算能通过若干次的“除数右移1位”和“从被除数或余数中减去除数”这两种操作完成。

如果我们再能设法将减法操作转化为某种形式的加法操作,那么加、减、乘、除运算就全部可以用“移位”和“相加”两种操作实现了。利用上述特点能使运算电路的结构大为简化。这也是数字电路中普遍采用二进制算术运算的重要原因之一。

### 1.4.2 反码、补码和补码运算

我们已经知道,在数字电路中是用逻辑电路输出的高、低电平表示二进制数的1和0的。那么数的正、负又如何表示呢?通常采用的方法是在二进制数的前面增加一位符号位。符号位为0表示这个数是正数,符号位为1表示这个数是负数。这种形式的数称为原码。

在做减法运算时,如果两个数是用原码表示的,则首先需要比较两数绝对值的大小,然后以绝对值大的一个作为被减数、绝对值小的一个作为减数,求出差值,并以绝对值大的一个数的符号作为差值的符号。不难看出,这个操作过程比较麻烦,而且需要使用数值比较电路和减法运算电路。如果能用两数的补码相加代替上述的减法运算,那么计算过程中就无需使用数值比较电路和减法运算电路了,从而使运算器的电路结构大为简化。

为了说明补码运算的原理,我们先来讨论一个生活中常见的事例。例如,你在5点钟的时候发现自己的手表停在10点上了,因而必须把表针拨回到5点。由图1.4.1可以看出,这时有两种拨法:第一种拨法是往回拨5格,10-5=5,拨回到了5点;另一种拨法是往前拨7格,10+7=17。由于表盘的最大数只有12,超过12以后的“进位”将自动消失,于是就只剩下减去12以后的余数了,即17-12=5,也将表针拨回到了5点。这个例子说明,10-5的减法运算可以用10+7的加法运算代替。因为5和7相加正好等于产生进位的模数12,所以我们称7为-5对模12的补数,也称为补码(Complement)。

图 1.4.1 说明补码运算原理的例子

从这个例子中可以得出一个结论,就是在舍弃进位的条件下,减去某个数可以用加上它的补码来代替。这个结论同样适用于二进制数的运算。

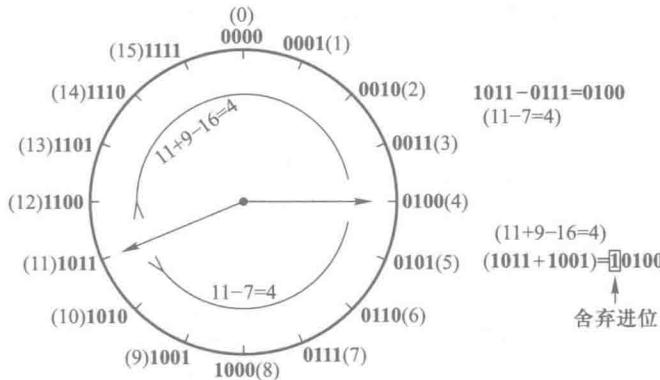

图 1.4.2 给出了 4 位二进制数补码运算的一个例子。由图可见, $1011 - 0111 = 0100$  的减法运算,在舍弃进位的条件下,可以用  $1011 + 1001 = 0100$  的加法运算代替。因为 4 位二进制数的进位基数是 16(**10000**),所以 **1001**(9)恰好是**-0111**(-7)对模 16 的补码。

图 1.4.2 4 位二进制数补码运算的例子

基于上述原理,对于有效数字(不包括符号位)为  $n$  位的二进制数  $N$ ,它的补码( $N$ )<sub>COMP</sub>表示方法为

$$(N)_{\text{COMP}} = \begin{cases} N & (\text{当 } N \text{ 为正数}) \\ 2^n - N & (\text{当 } N \text{ 为负数}) \end{cases} \quad (1.4.1)$$

即正数(当符号位为 **0** 时)的补码与原码相同,负数(当符号位为 **1** 时)的补码等于  $2^n - N$ 。符号位保持不变。

在一些国外的教材中,也将式(1.4.1)定义的补码称为“2 的补码”(2's Complement)。

为了避免在求补码的过程中做减法运算,通常是先求出  $N$  的反码( $N$ )<sub>INV</sub>,然后在负数的反码上加 1 而得到补码。二进制  $N$  的反码( $N$ )<sub>INV</sub>是这样定义的

$$(N)_{\text{INV}} = \begin{cases} N & (\text{当 } N \text{ 为正数}) \\ (2^n - 1) - N & (\text{当 } N \text{ 为负数}) \end{cases} \quad (1.4.2)$$

由上式可知,当  $N$  为负数时, $N + (N)_{\text{INV}} = 2^n - 1$ ,而  $2^n - 1$  是  $n$  位全为 **1** 的二进制数,所以只要将  $N$  中每一位的 **1** 改为 **0**、**0** 改为 **1**,就得到了( $N$ )<sub>INV</sub>。以后我们将会看到,将二进制数的每一位

求反，在电路上是很容易实现的。国外的有些教材中又将式(1.4.2)定义的反码称为“1的补码”(1's Complement)。

由式(1.4.2)又可得到，当  $N$  为负数时， $(N)_{INV} + 1 = 2^n - N$ ，而由式(1.4.1)又知，当  $N$  为负数时， $(N)_{COMP} = 2^n - N$ ，由此得到

$$(N)_{COMP} = (N)_{INV} + 1 \quad (1.4.3)$$

即二进制负数的补码等于它的反码加 1。

**【例 1.4.1】** 写出带符号位二进制数 **00011010** (+26)、**10011010** (-26)、**00101101** (+45) 和 **10101101** (-45) 的反码和补码。

解：根据式(1.4.2)和式(1.4.3)得到

| 原 码             | 反 码             | 补 码             |

|-----------------|-----------------|-----------------|

| <b>00011010</b> | <b>00011010</b> | <b>00011010</b> |

| <b>10011010</b> | <b>11100101</b> | <b>11100110</b> |

| <b>00101101</b> | <b>00101101</b> | <b>00101101</b> |

| <b>10101101</b> | <b>11010010</b> | <b>11010011</b> |

表 1.4.1 是带符号位的 3 位二进制数原码、反码和补码的对照表。其中规定用 **1000** 作为 -8 的补码，而不用来表示 -0。

表 1.4.1 原码、反码、补码对照表

| 十进制数 | 二进制数        |             |             |

|------|-------------|-------------|-------------|

|      | 原码(带符号数)    | 反 码         | 补 码         |

| +7   | <b>0111</b> | <b>0111</b> | <b>0111</b> |

| +6   | <b>0110</b> | <b>0110</b> | <b>0110</b> |

| +5   | <b>0101</b> | <b>0101</b> | <b>0101</b> |

| +4   | <b>0100</b> | <b>0100</b> | <b>0100</b> |

| +3   | <b>0011</b> | <b>0011</b> | <b>0011</b> |

| +2   | <b>0010</b> | <b>0010</b> | <b>0010</b> |

| +1   | <b>0001</b> | <b>0001</b> | <b>0001</b> |

| +0   | <b>0000</b> | <b>0000</b> | <b>0000</b> |

| -1   | <b>1001</b> | <b>1110</b> | <b>1111</b> |

| -2   | <b>1010</b> | <b>1101</b> | <b>1110</b> |

| -3   | <b>1011</b> | <b>1100</b> | <b>1101</b> |

| -4   | <b>1100</b> | <b>1011</b> | <b>1100</b> |

| -5   | <b>1101</b> | <b>1010</b> | <b>1011</b> |

| -6   | <b>1110</b> | <b>1001</b> | <b>1010</b> |

| -7   | <b>1111</b> | <b>1000</b> | <b>1001</b> |

| -8   | <b>1000</b> | <b>1111</b> | <b>1000</b> |

下面再来讨论两个用补码表示的二进制数相加时,和的符号位如何得到。为此,我们在例 1.4.2 中列举出了两数相加时的四种情况。

**【例 1.4.2】** 用二进制补码运算求出  $13+10$ 、 $13-10$ 、 $-13+10$  和  $-13-10$ 。

解: 由于  $13+10$  和  $-13-10$  的绝对值为 23, 所以必须用有效数字为 5 位的二进制数才能表示, 再加上一位符号位, 就得到 6 位的二进制补码。

由式(1.4.1)和式(1.4.3)可知,  $+13$  的二进制补码应为 **001101**(最高位为符号位),  $-13$  的二进制补码为 **110011**,  $+10$  的二进制补码为 **001010**,  $-10$  的二进制补码为 **110110**。计算结果分别为

$$\begin{array}{r} +13 \\ +10 \\ \hline +23 \end{array} \quad \begin{array}{r} 0 \ 01101 \\ 0 \ 01010 \\ \hline 0 \ 10111 \end{array} \quad \begin{array}{r} +13 \\ -10 \\ \hline +3 \end{array} \quad \begin{array}{r} 0 \ 01101 \\ 1 \ 10110 \\ \hline (1)0 \ 00011 \end{array}$$

$$\begin{array}{r} -13 \\ +10 \\ \hline -3 \end{array} \quad \begin{array}{r} 1 \ 10011 \\ 0 \ 01010 \\ \hline 1 \ 11101 \end{array} \quad \begin{array}{r} -13 \\ -10 \\ \hline -23 \end{array} \quad \begin{array}{r} 1 \ 10011 \\ 1 \ 10110 \\ \hline (1)1 \ 01001 \end{array}$$

从上面的例子中可以看出,若将两个加数的符号位和来自最高有效数位的进位相加,得到的结果(舍弃产生的进位)就是和的符号。这个道理仍然可以用图 1.4.2 所示的图形加以说明。

需要强调指出,在两个同符号数相加时,它们的绝对值之和不可超过有效数位所能表示的最大值,否则会得出错误的计算结果。

## 复习思考题

R1.4.1 二进制正、负数的原码、反码和补码三者之间是什么关系?

R1.4.2 为什么两个二进制数的补码相加时,和的符号位等于两数的符号位与来自最高有效数位的进位相加的结果(舍弃产生的进位)?

R1.4.3 如何求二进制数补码对应的原码?

## 1.5 几种常用的编码

### 一、十进制代码

为了用二进制代码表示十进制数的 0~9 这十个状态,二进制代码至少应当有 4 位。4 位二进制代码一共有十六个(**0000 ~ 1111**),取其中哪十个以及如何与 0~9 相对应,有许多种方案。表 1.5.1 中列出了常见的几种十进制代码,它们的编码规则各不相同。

表 1.5.1 几种常见的十进制代码

| 十进制数<br>/\ 编码种类 | 8421 码<br>(BCD 代码) | 余 3 码   | 2421 码  | 5211 码  | 余 3 循环码 |

|-----------------|--------------------|---------|---------|---------|---------|

| 0               | 0 0 0 0            | 0 0 1 1 | 0 0 0 0 | 0 0 0 0 | 0 0 1 0 |

| 1               | 0 0 0 1            | 0 1 0 0 | 0 0 0 1 | 0 0 0 1 | 0 1 1 0 |

| 2               | 0 0 1 0            | 0 1 0 1 | 0 0 1 0 | 0 1 0 0 | 0 1 1 1 |

| 3               | 0 0 1 1            | 0 1 1 0 | 0 0 1 1 | 0 1 0 1 | 0 1 0 1 |

| 4               | 0 1 0 0            | 0 1 1 1 | 0 1 0 0 | 0 1 1 1 | 0 1 0 0 |

| 5               | 0 1 0 1            | 1 0 0 0 | 1 0 1 1 | 1 0 0 0 | 1 1 0 0 |

| 6               | 0 1 1 0            | 1 0 0 1 | 1 1 0 0 | 1 0 0 1 | 1 1 0 1 |

| 7               | 0 1 1 1            | 1 0 1 0 | 1 1 0 1 | 1 1 0 0 | 1 1 1 1 |

| 8               | 1 0 0 0            | 1 0 1 1 | 1 1 1 0 | 1 1 0 1 | 1 1 1 0 |

| 9               | 1 0 0 1            | 1 1 0 0 | 1 1 1 1 | 1 1 1 1 | 1 0 1 0 |

| 权               | 8 4 2 1            |         | 2 4 2 1 | 5 2 1 1 |         |

8421 码又称 BCD(Binary Coded Decimal)码,是十进制代码中最常用的一种。在这种编码方式中,每一位二值代码的 1 都代表一个固定数值,将每一位的 1 代表的十进制数加起来,得到的结果就是它所代表的十进制数码。由于代码中从左到右每一位的 1 分别表示 8、4、2、1,所以将这种代码称为 8421 码。每一位的 1 代表的十进制数称为这一位的权。8421 码中每一位的权是固定不变的,它属于恒权代码。

余 3 码的编码规则与 8421 码不同,如果把每一个余 3 码看作 4 位二进制数,则它的数值要比它所表示的十进制数码多 3,故而将这种代码称为余 3 码。

如果将两个余 3 码相加,所得的和将比十进制数和所对应的二进制数多 6。因此,在用余 3 码做十进制加法运算时,若两数之和为 10,正好等于二进制数的 16,于是便从高位自动产生进位信号。

此外,从表 1.5.1 中还可以看出,0 和 9、1 和 8、2 和 7、3 和 6、4 和 5 的余 3 码互为反码,这对于求取对 10 的补码是很方便的。

余 3 码不是恒权代码。如果试图将每个代码视为二进制数,并使它等效的十进制数与所表示的代码相等,那么代码中每一位的 1 所代表的十进制数在各个代码中不能是固定的。

2421 码是一种恒权代码,它的 0 和 9、1 和 8、2 和 7、3 和 6、4 和 5 也互为反码,这个特点和余 3 码相仿。

5211 码是另一种恒权代码。待学了第六章中计数器的分频作用后可以发现,如果按 8421 码接成十进制计数器,则连续输入计数脉冲时,4 个触发器输出脉冲对于计数脉冲的分频比从低位到高位依次为 5:2:1:1。可见,5211 码每一位的权正好与 8421 码十进制计数器 4 个触发器输出脉冲的分频比相对应。这种对应关系在构成某些数字系统时很有用。

余 3 循环码是一种变权码,每一位的 1 在不同代码中并不代表固定的数值。它的主要特点是相邻的两个代码之间仅有一位的状态不同。

## 二、格雷码

格雷码(Gray Code)又称循环码。从表 1.5.2 的 4 位格雷码编码表中可以看出格雷码的构成方法,这就是每一位的状态变化都按一定的顺序循环。如果从 **0000** 开始,最右边一位的状态按 **0110** 顺序循环变化,右边第二位的状态按 **00111100** 顺序循环变化,右边第三位按 **00001111110000** 顺序循环变化。可见,自右向左,每一位状态循环中连续的 0、1 数目增加一倍。由于 4 位格雷码只有 16 个,所以最左边一位的状态只有半个循环,即 **0000000011111111**。按照上述原则,我们就很容易得到更多位数的格雷码。

与普通的二进制代码相比,格雷码的最大优点就在于当它按照表 1.5.2 的编码顺序依次变化时,相邻两个代码之间只有一位发生变化。这样在代码转换的过程中就不会产生过渡“噪声”。而在普通二进制代码的转换过程中,则有时会产生过渡噪声。例如,第四行的二进制代码 **0011** 转换为第五行的 **0100** 过程中,如果最右边一位的变化比其他两位的变化慢,就会在一个极短的瞬间出现 **0101** 状态,这个状态将成为转换过程中出现的噪声。而在第四行的格雷码 **0010** 向第五行的 **0110** 转换过程中则不会出现过渡噪声。这种过渡噪声在有些情况下甚至会影响电路的正常工作,这时就必须采取措施加以避免。在第 4.9 节中我们还将进一步讨论这个问题。

表 1.5.2 4 位格雷码与二进制代码的比较

| 编 码 顺 序 | 二进制代码       | 格 雷 码       |

|---------|-------------|-------------|

| 0       | <b>0000</b> | <b>0000</b> |

| 1       | <b>0001</b> | <b>0001</b> |

| 2       | <b>0010</b> | <b>0011</b> |

| 3       | <b>0011</b> | <b>0010</b> |

| 4       | <b>0100</b> | <b>0110</b> |

| 5       | <b>0101</b> | <b>0111</b> |

| 6       | <b>0110</b> | <b>0101</b> |

| 7       | <b>0111</b> | <b>0100</b> |

| 8       | <b>1000</b> | <b>1100</b> |

| 9       | <b>1001</b> | <b>1101</b> |

| 10      | <b>1010</b> | <b>1111</b> |

| 11      | <b>1011</b> | <b>1110</b> |

| 12      | <b>1100</b> | <b>1010</b> |

| 13      | <b>1101</b> | <b>1011</b> |

| 14      | <b>1110</b> | <b>1001</b> |

| 15      | <b>1111</b> | <b>1000</b> |

十进制代码中的余 3 循环码就是取 4 位格雷码中的十个代码组成的,它仍然具有格雷码的优点,即两个相邻代码之间仅有一位不同。

### 三、美国信息交换标准代码(ASCII)

美国信息交换标准代码(American Standard Code for Information Interchange,简称ASCII码)是由美国国家标准化协会(ANSI)制定的一种信息代码,广泛地用于计算机和通信领域中。ASCII码已经由国际标准化组织(ISO)认定为国际通用的标准代码。

ASCII码是一组7位二进制代码( $b_7b_6b_5b_4b_3b_2b_1$ ),共128个,其中包括表示0~9的十个代码,表示大、小写英文字母的52个代码,32个表示各种符号的代码以及34个控制码。表1.5.3是ASCII码的编码表,每个控制码在计算机操作中的含义列于表1.5.4中。

表1.5.3 美国信息交换标准代码(ASCII码)

| $b_4b_3b_2b_1$ | $b_7b_6b_5$ |     |     |     |     |     |     |     |

|----------------|-------------|-----|-----|-----|-----|-----|-----|-----|

|                | 000         | 001 | 010 | 011 | 100 | 101 | 110 | 111 |

| 0000           | NUL         | DLE | SP  | 0   | @   | P   | 、   | p   |

| 0001           | SOH         | DC1 | !   | 1   | A   | Q   | a   | q   |

| 0010           | STX         | DC2 | “   | 2   | B   | R   | b   | r   |

| 0011           | ETX         | DC3 | #   | 3   | C   | S   | c   | s   |

| 0100           | EOT         | DC4 | \$  | 4   | D   | T   | d   | t   |

| 0101           | ENQ         | NAK | %   | 5   | E   | U   | e   | u   |

| 0110           | ACK         | SYN | &   | 6   | F   | V   | f   | v   |

| 0111           | BEL         | ETB | ‘   | 7   | G   | W   | g   | w   |

| 1000           | BS          | CAN | (   | 8   | H   | X   | h   | x   |

| 1001           | HT          | EM  | )   | 9   | I   | Y   | i   | y   |

| 1010           | LF          | SUB | *   | :   | J   | Z   | j   | z   |

| 1011           | VT          | ESC | +   | ;   | K   | [   | k   |     |

| 1100           | FF          | FS  | ,   | <   | L   | \   | l   |     |

| 1101           | CR          | GS  | -   | =   | M   | ]   | m   |     |

| 1110           | SO          | RS  | .   | >   | N   | ^   | n   | ~   |

| 1111           | SI          | US  | /   | ?   | O   | -   | o   | DEL |

表1.5.4 ASCII码中控制码的含义

| 代 码 | 含 义                 |

|-----|---------------------|

| NUL | Null                |

| SOH | Start of heading    |

| STX | Start of text       |

| ETX | End of text         |

| EOT | End of transmission |

| ENQ | Enquiry             |

续表

| 代 码 | 含 义                               |

|-----|-----------------------------------|

| ACK | Acknowledge 承认                    |

| BEL | Bell 报警                           |

| BS  | Backspace 退格                      |

| HT  | Horizontal tab 横向制表               |

| LF  | Line feed 换行                      |

| VT  | Vertical tab 垂直制表                 |

| FF  | Form feed 换页                      |

| CR  | Carriage return 回车                |

| SO  | Shift out 移出                      |

| SI  | Shift in 移入                       |

| DLE | Date Link escape 数据通信换码           |

| DC1 | Device control 1 设备控制 1           |

| DC2 | Device control 2 设备控制 2           |

| DC3 | Device control 3 设备控制 3           |

| DC4 | Device control 4 设备控制 4           |

| NAK | Negative acknowledge 否定           |

| SYN | Synchronous idle 空转同步             |

| ETB | End of transmission block 信息块传输结束 |

| CAN | Cancel 作废                         |

| EM  | End of medium 媒体用毕                |

| SUB | Substitute 代替,置换                  |

| ESC | Escape 扩展                         |

| FS  | File separator 文件分隔               |

| GS  | Group separator 组分隔               |

| RS  | Record separator 记录分隔             |

| US  | Unit separator 单元分隔               |

| SP  | Space 空格                          |

| DEL | Delete 删除                         |

### 复习思考题

R1.5.1 8421 码、2421 码、5211 码、余 3 码和余 3 循环码在编码规则上各有何特点?

R1.5.2 你能写出 3 位和 5 位格雷码的顺序编码吗?

R1.5.3 你能用 ASCII 代码写出“Welcome!”吗?

## 本 章 小 结

不同的数码既可以用来表示不同数量的大小,又可以用来表示不同的事物。

在用数码表示数量的大小时,采用的各种计数进位制规则称为数制。常用的数制有十进制、二进制、八进制和十六进制几种。各种进制所表示的数值可以按照本章介绍的方法互相转换。

由于数字电路的基本运算都采用二进制运算,所以这一章里还比较详细地介绍了二进制数的符号在数字电路中的表示方法,原码、反码和补码的概念,以及采用补码进行带符号数加法运算的原理。

在用数码表示不同的事物时,这些数码已没有数量大小的含义,所以将它们称为代码。本章中所列举的十进制代码、格雷码、ASCII 码是几种常见的通用代码。此外,我们完全可以根据自己的需要,自行编制专用的代码。

## 习 题

[题 1.1] 为了将 600 份文件顺序编码,如果采用二进制代码,最少需要用几位? 如果改用八进制或十六进制代码,则最少各需要用几位?

[题 1.2] 将下列二进制整数转换为等值的十进制数。

$$(1) (01101)_2; \quad (2) (10100)_2; \quad (3) (10010111)_2; \quad (4) (1101101)_2.$$

[题 1.3] 将下列二进制小数转换为等值的十进制数。

$$(1) (0.1001)_2; \quad (2) (0.0111)_2; \quad (3) (0.101101)_2; \quad (4) (0.001111)_2.$$

[题 1.4] 将下列二进制数转换为等值的十进制数。

$$(1) (101.011)_2; \quad (2) (110.101)_2; \quad (3) (1111.1111)_2; \quad (4) (1001.0101)_2.$$

[题 1.5] 将下列二进制数转换为等值的八进制数和十六进制数。

$$(1) (1110.0111)_2; \quad (2) (1001.1101)_2; \quad (3) (0110.1001)_2; \quad (4) (101100.110011)_2.$$

[题 1.6] 将下列十六进制数转换为等值的二进制数。

$$(1) (8C)_{16}; \quad (2) (3D.BE)_{16}; \quad (3) (8F.FF)_{16}; \quad (4) (10.00)_{16}.$$

[题 1.7] 将下列十进制数转换为等值的二进制数和十六进制数。

$$(1) (17)_{10}; \quad (2) (127)_{10}; \quad (3) (79)_{10}; \quad (4) (255)_{10}.$$

[题 1.8] 将下列十进制数转换为等值的二进制数和十六进制数。要求二进制数保留小数点以后 8 位有效数字。

$$(1) (0.519)_{10}; \quad (2) (0.251)_{10}; \quad (3) (0.0376)_{10}; \quad (4) (0.5128)_{10}.$$

[题 1.9] 将下列十进制数转换为等值的二进制数和十六进制数。要求二进制数保留小数点以后 4 位有效数字。

$$(1) (25.7)_{10}; \quad (2) (188.875)_{10}; \quad (3) (107.39)_{10}; \quad (4) (174.06)_{10}.$$

[题 1.10] 写出下列二进制数的原码、反码和补码。

$$(1) (+1011)_2; \quad (2) (+00110)_2; \quad (3) (-1101)_2; \quad (4) (-00101)_2.$$

[题 1.11] 写出下列带符号位二进制数(最高位为符号位)的反码和补码。

$$(1) (011011)_2; \quad (2) (001010)_2; \quad (3) (111011)_2; \quad (4) (101010)_2.$$

[题 1.12] 用 8 位的二进制补码表示下列十进制数。

$$(1) +17; \quad (2) +28; \quad (3) -13; \quad (4) -47; \quad (5) -89; \quad (6) -121.$$

[题 1.13] 计算下列用补码表示的二进制数的代数和。如果和为负数,请求出负数的绝对值。

$$(1) 01001101+00100110; \quad (2) 00011101+01001100;$$

$$(3) 00110010+10000011; \quad (4) 00011110+10011100;$$

$$(5) 11011101+01001011; \quad (6) 10011101+01100110;$$

$$(7) 11100111+11011011; \quad (8) 11111001+10001000.$$

[题 1.14] 用二进制补码运算计算下列各式。式中的 4 位二进制数是不带符号位的绝对值。如果和为负数,请求出负数的绝对值。(提示:所用补码的有效位数应足够表示代数和的最大绝对值。)

$$(1) 1010+0011; \quad (2) 1101+1011;$$

$$(3) 1010-0011; \quad (4) 1101-1011;$$

$$(5) 0011-1010; \quad (6) 1011-1101;$$

$$(7) -0011-1010; \quad (8) -1101-1011.$$

[题 1.15] 用二进制补码运算计算下列各式。(提示:所用补码的有效位数应足够表示代数和的最大绝对值。)

$$(1) 3+15; \quad (2) 8+11; \quad (3) 12-7; \quad (4) 23-11;$$

$$(5) 9-12; \quad (6) 20-25; \quad (7) -12-5; \quad (8) -16-14.$$

## 第二章

# 逻辑代数基础

### 内容提要

本章介绍用于分析数字电路逻辑功能的数学方法——逻辑代数。首先将介绍逻辑代数的基本公式、常用公式和几个重要的定理，然后讲授逻辑函数的各种描述方法以及这些描述方法之间的互相转换。最后，介绍逻辑函数的化简方法。

## 2.1 概述

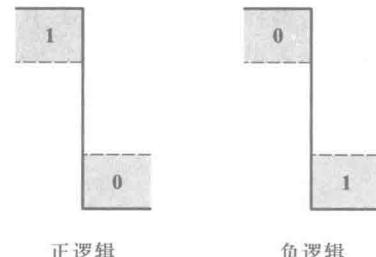

在上一章中我们已经讲过，不同的数码不仅可以表示数量的不同大小，而且还能用来表示不同的事物。在数字逻辑电路中，用 1 位二进制数码的 0 和 1 表示一个事物的两种不同逻辑状态。例如，可以用 1 和 0 分别表示一件事情的是和非、真和假、有和无、好和坏，或者表示电路的通和断、电灯的亮和暗、门的开和关等等。这种只有两种对立逻辑状态的逻辑关系称为二值逻辑。

所谓“逻辑”，在这里是指事物间的因果关系。当两个二进制数码表示不同的逻辑状态时，它们之间可以按照指定的某种因果关系进行推理运算。我们将这种运算称为逻辑运算。

1849 年英国数学家乔治·布尔(George Boole)首先提出了进行逻辑运算的数学方法——布尔代数。后来，由于布尔代数被广泛应用于解决开关电路和数字逻辑电路的分析与设计中，所以也将布尔代数称为开关代数或逻辑代数。本章所讲的逻辑代数就是布尔代数在二值逻辑电路中的应用。下面我们将看到，虽然有些逻辑代数的运算公式在形式上和普通代数的运算公式雷同，但是两者所包含的物理意义有本质的不同。逻辑代数中也用字母表示变量，这种变量称为逻辑变量。逻辑运算表示的是逻辑变量以及常量之间逻辑状态的推理运算，而不是数量之间的运算。

虽然在二值逻辑中，每个变量的取值只有 0 和 1 两种可能，只能表示两种不同的逻辑状态，但是我们可以用多变量的不同状态组合表示事物的多种逻辑状态，处理任何复杂的逻辑问题。

## 2.2 逻辑代数中的三种基本运算

逻辑代数的基本运算有与(AND)、或(OR)、非(NOT)三种。为便于理解它们的含义，先来

看一个简单的例子。

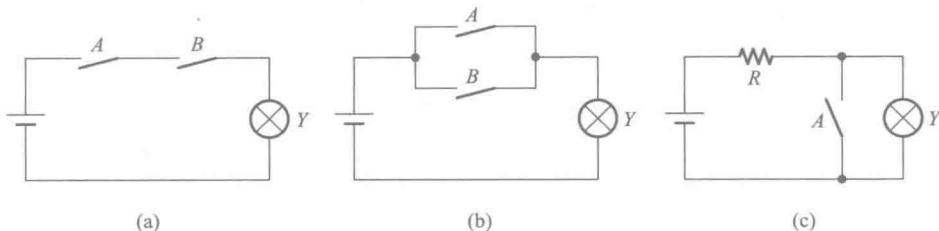

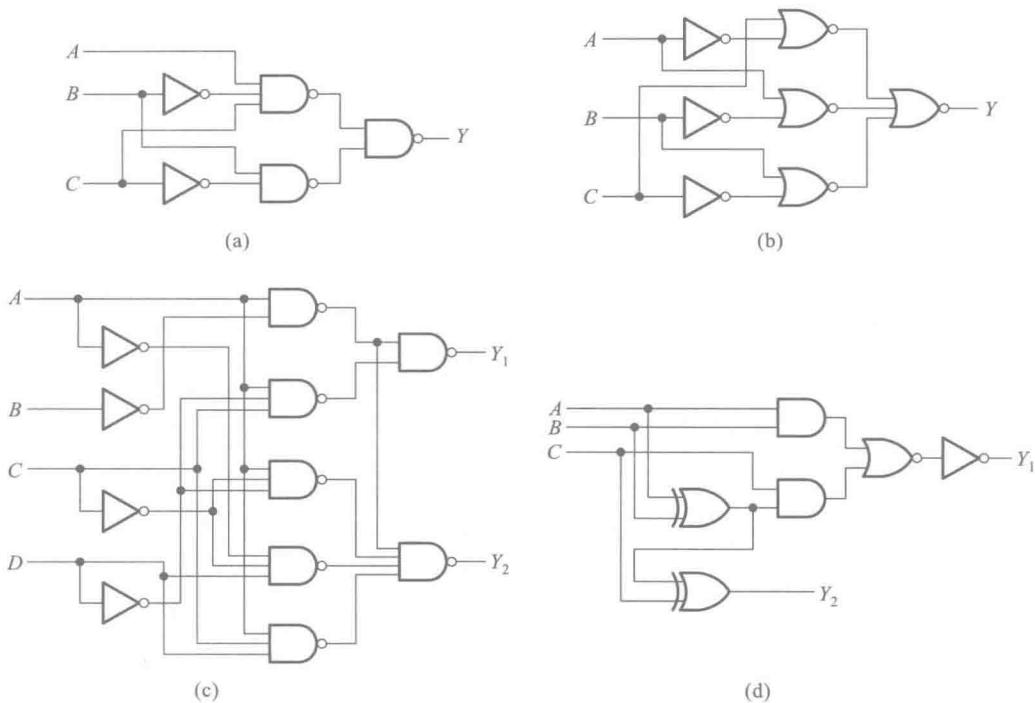

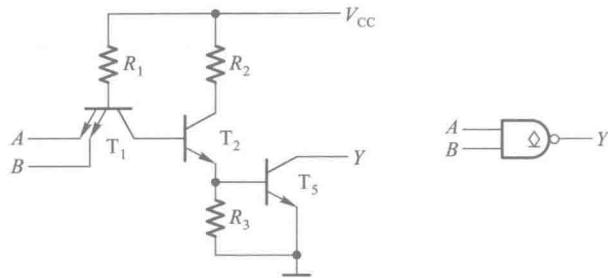

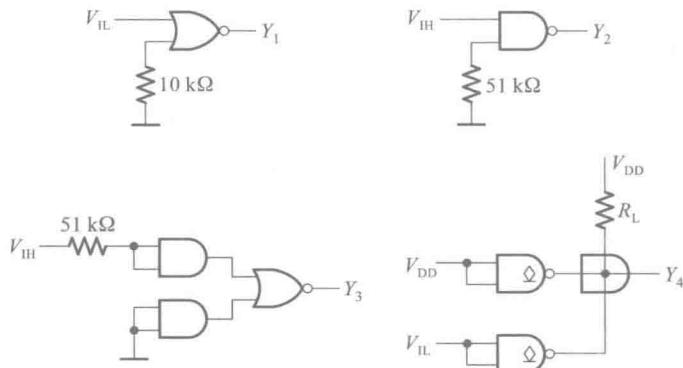

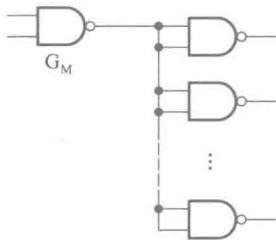

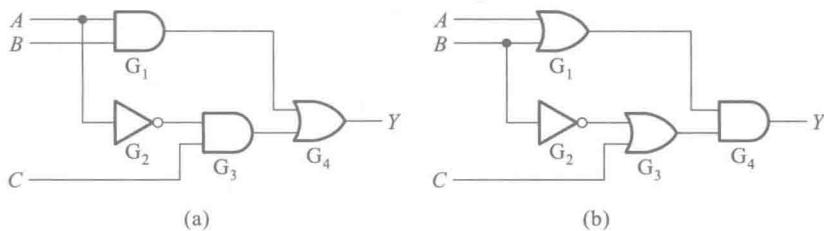

图 2.2.1 中给出了三个指示灯的控制电路。在图(a)电路中,只有当两个开关同时闭合时,指示灯才会亮;在图(b)电路中,只要有任何一个开关闭合,指示灯就亮;而在图(c)电路中,开关断开时灯亮,开关闭合时灯反而不亮。

图 2.2.1 用于说明与、或、非定义的电路

如果把开关闭合作为条件(或导致事物结果的原因),把灯亮作为结果,那么图 2.2.1 中的三个电路代表了三种不同的因果关系:

图(a)的例子表明,只有决定事物结果的全部条件同时具备时,结果才发生。这种因果关系称为逻辑与,或称逻辑相乘。

图(b)的例子表明,在决定事物结果的诸条件中只要有任何一个满足,结果就会发生。这种因果关系称为逻辑或,也称逻辑相加。

图(c)的例子表明,只要条件具备了,结果便不会发生;而条件不具备时,结果一定发生。这种因果关系称为逻辑非,也称逻辑求反。

若以  $A$ 、 $B$  表示开关的状态,并以 1 表示开关闭合,以 0 表示开关断开;以  $Y$  表示指示灯的状态,并以 1 表示灯亮,以 0 表示不亮,则可以列出以 0、1 表示的与、或、非逻辑关系的图表,如表 2.2.1、表 2.2.2 和表 2.2.3 所示。这种图表称为逻辑真值表(truth table),简称真值表。

表 2.2.1 与逻辑

运算的真值表

| $A$ | $B$ | $Y$ |

|-----|-----|-----|

| 0   | 0   | 0   |

| 0   | 1   | 0   |

| 1   | 0   | 0   |

| 1   | 1   | 1   |

表 2.2.2 或逻辑

运算的真值表

| $A$ | $B$ | $Y$ |

|-----|-----|-----|

| 0   | 0   | 0   |

| 0   | 1   | 1   |

| 1   | 0   | 1   |

| 1   | 1   | 1   |

表 2.2.3 非逻辑

运算的真值表

| $A$ | $Y$ |

|-----|-----|

| 0   | 1   |

| 1   | 0   |

在逻辑代数中,将与、或、非看作是逻辑变量  $A$ 、 $B$  间的三种最基本的逻辑运算,并以“·”表示与运算,以“+”表示或运算,以变量右上角的“'”表示非运算。因此, $A$  和  $B$  进行与逻辑运算时可写成

$$Y = A \cdot B \quad (2.2.1)$$

$A$  和  $B$  进行或逻辑运算时可写成

$$Y = A + B \quad (2.2.2)$$

对  $A$  进行非逻辑运算时可写成

$$Y = A' \quad (2.2.3)$$

同时,将实现与逻辑运算的单元电路称为与门,将实现或逻辑运算的单元电路称为或门,将实现非逻辑运算的单元电路称为非门(也称为反相器)。

逻辑非的运算符号尚无统一的标准。除了本书中采用“ $'$ ”表示非运算以外,目前在国内、外的某些电子技术教材和 EDA 软件中,也采用  $\bar{A}$ 、 $\sim A$ 、 $\neg A$  表示  $A$  的非运算。用“ $'$ ”作为非运算符号比起在变量上加横线作为非运算符号更便于计算机输入,尤其在逻辑运算式中存在多重非运算时,这种优越性就更加明显。因此,在教材和 EDA 软件中使用“ $'$ ”作为非运算符号的越来越多了。

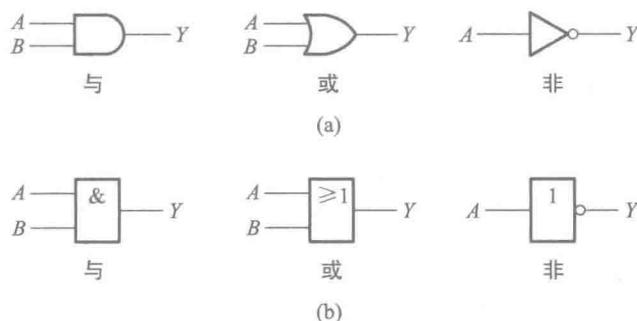

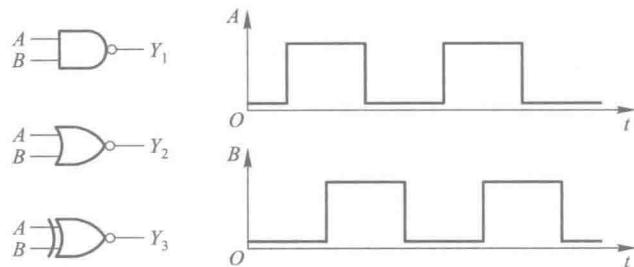

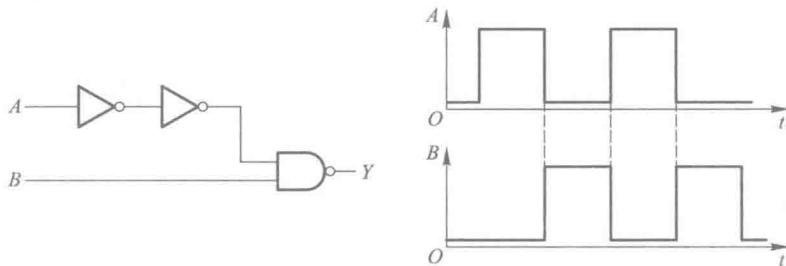

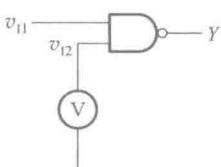

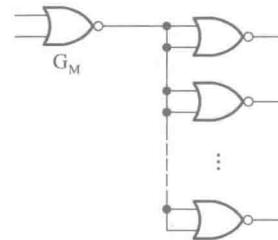

与、或、非逻辑运算还可以用图形符号表示。图 2.2.2 中给出了被 IEEE(电气与电子工程师协会)和 IEC(国际电工协会)认定的两套与、或、非的图形符号,其中一套是目前在国外教材和 EDA 软件中普遍使用的特定外形符号,如图 2.2.2(a) 所示。另一套是矩形轮廓的符号,如图 2.2.2(b) 所示。本书中采用特定外形符号。

图 2.2.2 与、或、非的图形符号

(a) 特定外形符号 (b) 矩形轮廓符号

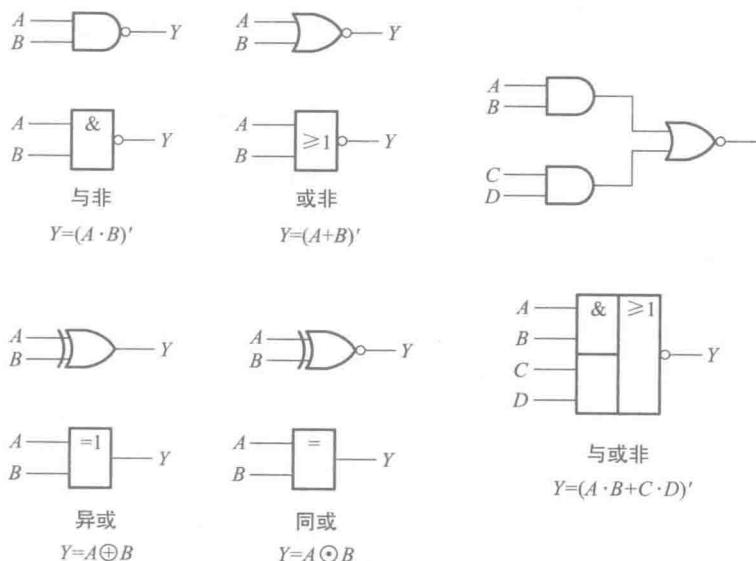

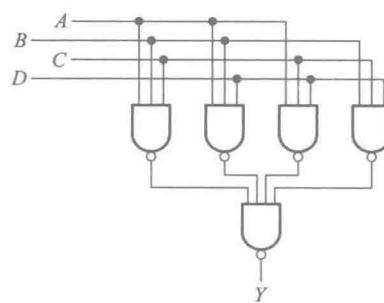

实际的逻辑问题往往比与、或、非复杂得多,不过它们都可以用与、或、非的组合来实现。最常见的复合逻辑运算有与非(NAND)、或非(NOR)、与或非(AND-NOR)、异或(EXCLUSIVE OR)、同或(EXCLUSIVE NOR)等。表 2.2.4~表 2.2.8 给出了这些复合逻辑运算的真值表。图 2.2.3 是它们的图形逻辑符号和运算符号。这些图形符号同样也有特定外形符号和矩形轮廓符号两种。

表 2.2.4 与非逻辑的真值表

| $A$ | $B$ | $Y$ |

|-----|-----|-----|

| 0   | 0   | 1   |

| 0   | 1   | 1   |

| 1   | 0   | 1   |

| 1   | 1   | 0   |

表 2.2.5 或非逻辑的真值表

| $A$ | $B$ | $Y$ |

|-----|-----|-----|

| 0   | 0   | 1   |

| 0   | 1   | 0   |

| 1   | 0   | 0   |

| 1   | 1   | 0   |

表 2.2.6 与或非逻辑的真值表

| A | B | C | D | Y |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 0 | 1 | 1 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 0 | 1 | 1 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 | 0 |

表 2.2.7 异或逻辑的真值表

| A | B | Y |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

表 2.2.8 同或逻辑的真值表

| A | B | Y |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

图 2.2.3 复合逻辑的图形符号和运算符号

由表 2.2.4 可见, 将  $A$ 、 $B$  先进行与运算, 然后将结果求反, 最后得到的即为  $A$ 、 $B$  的与非运算结果。因此, 可以把与非运算看作是与运算和非运算的组合。图 2.2.3 中图形符号上的小圆圈表示非运算。

在与或非逻辑中,  $A, B$  之间以及  $C, D$  之间都是与的关系, 只要  $A, B$  或  $C, D$  任何一组同时为 1, 输出  $Y$  就是 0。只有当每一组输入都不全是 1 时, 输出  $Y$  才是 1。

异或是这样一种逻辑关系: 当  $A, B$  不同时, 输出  $Y$  为 1; 而当  $A, B$  相同时, 输出  $Y$  为 0。异或也可以用与、或、非的组合表示。

$$A \oplus B = A \cdot B' + A' \cdot B \quad (2.2.4)$$

同或和异或相反, 当  $A, B$  相同时,  $Y$  等于 1,  $A, B$  不同时,  $Y$  等于 0。同或也可以写成与、或、非的组合形式

$$A \odot B = A \cdot B + A' \cdot B' \quad (2.2.5)$$

而且, 由表 2.2.7 和表 2.2.8 可见, 异或和同或互为反运算, 即

$$A \oplus B = (A \odot B)'; A \odot B = (A \oplus B)' \quad (2.2.6)$$

为简化书写, 允许将  $A \cdot B$  简写成  $AB$ , 略去逻辑相乘的运算符号“·”。

### 复习思考题

R2.2.1 你能各举出一个现实生活中存在的与、或、非逻辑关系的事例吗?

R2.2.2 两个变量的异或运算和同或运算之间是什么关系?

## 2.3 逻辑代数的基本公式和常用公式

### 2.3.1 基本公式

表 2.3.1 给出了逻辑代数的基本公式。这些公式也称为布尔恒等式。

表 2.3.1 逻辑代数的基本公式

| 序号 | 公 式                                         | 序号 | 公 式                                 |

|----|---------------------------------------------|----|-------------------------------------|

| 1  | $0 \cdot A = 0$                             | 10 | $1' = 0; 0' = 1$                    |

| 2  | $1 \cdot A = A$                             | 11 | $1 + A = 1$                         |

| 3  | $A \cdot A = A$                             | 12 | $0 + A = A$                         |

| 4  | $A \cdot A' = 0$                            | 13 | $A + A = A$                         |

| 5  | $A \cdot B = B \cdot A$                     | 14 | $A + A' = 1$                        |

| 6  | $A \cdot (B \cdot C) = (A \cdot B) \cdot C$ | 15 | $A + B = B + A$                     |

| 7  | $A \cdot (B+C) = A \cdot B + A \cdot C$     | 16 | $A + (B+C) = (A+B) + C$             |

| 8  | $(A \cdot B)' = A' + B'$                    | 17 | $A + B \cdot C = (A+B) \cdot (A+C)$ |

| 9  | $(A')' = A$                                 | 18 | $(A+B)' = A' \cdot B'$              |

式(1)、(2)、(11)和(12)给出了变量与常量间的运算规则。

式(3)和(13)是同一变量的运算规律, 也称为重叠律。

式(4)和(14)表示变量与它的反变量之间的运算规律,也称为互补律。

式(5)和(15)为交换律,式(6)和(16)为结合律,式(7)和(17)为分配律。

式(8)和(18)是著名的德·摩根(De.Morgan)定理,亦称反演律。在逻辑函数的化简和变换中经常要用到这一对公式。

式(9)表明,一个变量经过两次求反运算之后还原为其本身,所以该式又称为还原律。

式(10)是对 0 和 1 求反运算的规则,它说明 0 和 1 互为求反的结果。

这些公式的正确性可以用列真值表的方法加以验证。如果等式成立,那么将任何一组变量的取值代入公式两边所得的结果应该相等。因此,等式两边所对应的真值表也必然相同。

**【例 2.3.1】** 用真值表证明表 2.3.1 中式(17)的正确性。

解: 已知表 2.3.1 中的式(17)为

$$A+B \cdot C = (A+B) \cdot (A+C)$$

将 A、B、C 所有可能的取值组合逐一代入上式的两边,算出相应的结果,即得到表 2.3.2 所示的真值表。可见,等式两边对应的真值表相同,故等式成立。

表 2.3.2 式(17)的真值表

| A | B | C | $B \cdot C$ | $A+B \cdot C$ | $A+B$ | $A+C$ | $(A+B) \cdot (A+C)$ |

|---|---|---|-------------|---------------|-------|-------|---------------------|

| 0 | 0 | 0 | 0           | 0             | 0     | 0     | 0                   |

| 0 | 0 | 1 | 0           | 0             | 0     | 1     | 0                   |

| 0 | 1 | 0 | 0           | 0             | 1     | 0     | 0                   |

| 0 | 1 | 1 | 1           | 1             | 1     | 1     | 1                   |

| 1 | 0 | 0 | 0           | 1             | 1     | 1     | 1                   |

| 1 | 0 | 1 | 0           | 1             | 1     | 1     | 1                   |

| 1 | 1 | 0 | 0           | 1             | 1     | 1     | 1                   |

| 1 | 1 | 1 | 1           | 1             | 1     | 1     | 1                   |

## 2.3.2 若干常用公式

表 2.3.3 中列出了几个常用公式。这些公式是利用基本公式导出的。直接运用这些导出公式可以给化简逻辑函数的工作带来很大方便。

表 2.3.3 若干常用公式

| 序号 | 公 式                                                                                                                      |

|----|--------------------------------------------------------------------------------------------------------------------------|

| 21 | $A+A \cdot B = A$                                                                                                        |

| 22 | $A+A' \cdot B = A+B$                                                                                                     |

| 23 | $A \cdot B + A \cdot B' = A$                                                                                             |

| 24 | $A \cdot (A+B) = A$                                                                                                      |

| 25 | $A \cdot B + A' \cdot C + B \cdot C = A \cdot B + A' \cdot C$<br>$A \cdot B + A' \cdot C + BCD = A \cdot B + A' \cdot C$ |

| 26 | $A \cdot (A \cdot B)' = A \cdot B'; A' \cdot (AB)' = A'$                                                                 |

现将表 2.3.3 中的各式证明如下。

1. 式(21)  $A+A \cdot B = A$

证明： $A+A \cdot B = A \cdot (1+B) = A \cdot 1 = A$

上式说明，在两个乘积项相加时，若其中一项以另一项为因子，则该项是多余的，可以删去。

2. 式(22)  $A+A' \cdot B = A+B$

证明： $A+A' \cdot B = (A+A') \cdot (A+B) = 1 \cdot (A+B) = A+B$

这一结果表明，两个乘积项相加时，如果一项取反后是另一项的因子，则此因子是多余的，可以消去。

3. 式(23)  $A \cdot B+A \cdot B' = A$

证明： $A \cdot B+A \cdot B' = A(B+B') = A \cdot 1 = A$

这个公式的含义是，当两个乘积项相加时，若它们分别包含  $B$  和  $B'$  两个因子而其他因子相同，则两项定能合并，且可将  $B$  和  $B'$  两个因子消去。

4. 式(24)  $A \cdot (A+B) = A$

证明： $A \cdot (A+B) = A \cdot A + A \cdot B = A + A \cdot B$

$$= A \cdot (1+B) = A \cdot 1 = A$$

该式说明，变量  $A$  和包含  $A$  的和相乘时，其结果等于  $A$ ，即可以将和消掉。

5. 式(25)  $A \cdot B+A' \cdot C+B \cdot C = A \cdot B+A' \cdot C$

证明：

$$\begin{aligned} A \cdot B+A' \cdot C+B \cdot C &= A \cdot B+A' \cdot C+B \cdot C(A+A') \\ &= A \cdot B+A' \cdot C+A \cdot B \cdot C+A' \cdot B \cdot C \\ &= A \cdot B \cdot (1+C)+A' \cdot C \cdot (1+B) \\ &= A \cdot B+A' \cdot C \end{aligned}$$

这个公式说明，若两个乘积项中分别包含  $A$  和  $A'$  两个因子，而这两个乘积项的其余因子组成第三个乘积项时，则第三个乘积项是多余的，可以消去。

从上式不难进一步导出

$$A \cdot B+A' \cdot C+B \cdot C \cdot D = A \cdot B+A' \cdot C$$

6. 式(26)  $A \cdot (A \cdot B)' = A \cdot B'; A' \cdot (A \cdot B)' = A'$

证明： $A \cdot (A \cdot B)' = A \cdot (A'+B') = A \cdot A'+A \cdot B' = A \cdot B'$

上式说明，当  $A$  和一个乘积项的非相乘，且  $A$  为乘积项的因子时，则  $A$  这个因子可以消去。

$$\begin{aligned} A' \cdot (A \cdot B)' &= A' \cdot (A'+B') = A' \cdot A'+A' \cdot B' = A' \cdot (1+B') \\ &= A' \end{aligned}$$

此式表明，当  $A'$  和一个乘积项的非相乘，且  $A$  为乘积项的因子时，其结果就等于  $A'$ 。

从以上的证明可以看到，这些常用公式都是从基本公式导出的结果。当然，还可以推导出更多的常用公式。

### 复习思考题

R2.3.1 在逻辑代数的基本公式当中哪些公式的运算规则和普通代数的运算规则是相同的？哪些是不同的，需要特别记住的？

## 2.4 逻辑代数的基本定理

### 2.4.1 代入定理

在任何一个包含变量  $A$  的逻辑等式中,若以另外一个逻辑式代入式中所有  $A$  的位置,则等式仍然成立。这就是所谓的代入定理。

因为变量  $A$  仅有 **0** 和 **1** 两种可能的状态,所以无论将  $A=0$  还是  $A=1$  代入逻辑等式,等式都一定成立。而任何一个逻辑式的取值也不外 **0** 和 **1** 两种,所以用它取代式中的  $A$  时,等式自然也成立。因此,可以将代入定理看作无需证明的公理。

利用代入定理很容易把表 2.3.1 中的基本公式和表 2.3.3 中的常用公式推广为多变量的形式。

**【例 2.4.1】** 用代入定理证明德·摩根定理也适用于多变量的情况。

解: 已知二变量的德·摩根定理为

$$(A+B)' = A' \cdot B' \quad \text{及} \quad (A \cdot B)' = A' + B'$$

今以  $(B+C)$  代入左边等式中  $B$  的位置,同时以  $(B \cdot C)$  代入右边等式中  $B$  的位置,于是得到

$$\begin{aligned}(A+(B+C))' &= A' \cdot (B+C)' = A' \cdot B' \cdot C' \\ (A \cdot (B \cdot C))' &= A' + (B \cdot C)' = A' + B' + C'\end{aligned}$$

对一个乘积项或逻辑式求反时,应在乘积项或逻辑式外边加括号,然后对括号内的整个内容求反。

此外,在对复杂的逻辑式进行运算时,仍需遵守与普通代数一样的运算优先顺序,即先算括号里的内容,其次算乘法,最后算加法。

### 2.4.2 反演定理

对于任意一个逻辑式  $Y$ ,若将其中所有的“ $\cdot$ ”换成“ $+$ ”,“ $+$ ”换成“ $\cdot$ ”,**0** 换成 **1**,**1**换成**0**,原变量换成反变量,反变量换成原变量,则得到的结果就是  $Y'$ 。这个规律称为反演定理。

反演定理为求取已知逻辑式的反逻辑式提供了方便。

在使用反演定理时,还需注意遵守以下两个规则:

- ① 仍需遵守“先括号、然后乘、最后加”的运算优先次序。

- ② 不属于单个变量上的反号应保留不变。

回顾一下 2.3.1 节中讲过的德·摩根定理便可发现,它只不过是反演定理的一个特例而已。正是由于这个原因,才将它称为反演律。

**【例 2.4.2】** 已知  $Y=A(B+C)+CD$ ,求  $Y'$ 。

解: 根据反演定理可写出

$$\begin{aligned}

Y' &= (A'+B'C')(C'+D') \\

&= A'C'+B'C'+A'D'+B'C'D' \\

&= A'C'+B'C'+A'D'

\end{aligned}$$

如果利用基本公式和常用公式进行运算,也能得到同样的结果,但是要麻烦得多。

**【例 2.4.3】** 若  $Y=((AB'+C)'+D)'+C$ , 求  $Y'$ 。

解: 依据反演定理可直接写出

$$\begin{aligned}

Y' &= (((A'+B)C')'D')'C' \\

&= ((A'C'+BC')+D)C' \\

&= A'C'+BC'+C'D

\end{aligned}$$

### 2.4.3 对偶定理

若两逻辑式相等,则它们的对偶式也相等,这就是对偶定理。

所谓对偶式是这样定义的:对于任何一个逻辑式  $Y$ ,若将其中的“·”换成“+”,“+”换成“·”,0换成1,1换成0,则得到一个新的逻辑式  $Y^D$ ,这个  $Y^D$  就称为  $Y$  的对偶式,或者说  $Y$  和  $Y^D$  互为对偶式。

例如,若  $Y=A(B+C)$ , 则  $Y^D=A+BC$

若  $Y=(AB+CD)'$ , 则  $Y^D=((A+B)(C+D))'$

若  $Y=AB+(C+D)'$ , 则  $Y^D=(A+B)(CD)'$

为了证明两个逻辑式相等,也可以通过证明它们的对偶式相等来完成,因为有些情况下证明它们的对偶式相等更加容易。

**【例 2.4.4】** 试证明表 2.3.1 中的式(17),即

$$A+BC=(A+B)(A+C)$$

解: 首先写出等式两边的对偶式,得到

$$A(B+C) \text{ 和 } AB+AC$$

根据乘法分配律可知,这两个对偶式是相等的,亦即  $A(B+C)=AB+AC$ 。由对偶定理即可确定原来的两式也一定相等,于是式(17)得到证明。

如果仔细分析一下表 2.3.1 就能够发现,其中的公式(1)和(11)、(2)和(12)、(3)和(13)、(4)和(14)、(5)和(15)、(6)和(16)、(7)和(17)、(8)和(18)皆互为对偶式。因此,只要能证明公式(1)~(8)成立,则公式(11)~(18)已无需另做证明。

### 复习思考题

R2.4.1 代入定理中对代入逻辑式的形式和复杂程度有无限制?

R2.4.2 利用反演定理对给定逻辑式求反时,应如何处理变换的优先顺序和式中所有的非运算符号?

## 2.5 逻辑函数及其描述方法

### 2.5.1 逻辑函数

从上面讲过的各种逻辑关系中可以看到,如果以逻辑变量作为输入,以运算结果作为输出,那么当输入变量的取值确定之后,输出的取值便随之而定。因此,输出与输入之间乃是一种函数关系。这种函数关系称为逻辑函数(logic function),写作

$$Y=F(A,B,C,\dots)$$

由于变量和输出(函数)的取值只有 0 和 1 两种状态,所以我们所讨论的都是二值逻辑函数。

任何一件具体的因果关系都可以用一个逻辑函数来描述。例如,图 2.5.1 所示是一个举重裁判电路,可以用一个逻辑函数描述它的逻辑功能。

比赛规则规定,在一名主裁判和两名副裁判中,必须有两人以上(而且必须包括主裁判)认定运动员的动作合格,试举才算成功。比赛时主裁判掌握着开关 A,两名副裁判分别掌握着开关 B 和 C。当运动员举起杠铃时,裁判认为动作合格了就合上开关,否则不合。显然,指示灯 Y 的状态(亮与暗)是开关 A、B、C 状态(合上与断开)的函数。

若以 1 表示开关闭合,0 表示开关断开;以 1 表示灯亮,以 0 表示灯暗,则指示灯 Y 是开关 A、B、C 的二值逻辑函数,即

$$Y=F(A,B,C)$$

### 2.5.2 逻辑函数的描述方法

常用的逻辑函数描述方法有逻辑真值表、逻辑函数式(简称逻辑式或函数式)、逻辑图、波形图、卡诺图和硬件描述语言等。这一节只介绍前面四种方法,用卡诺图和硬件描述语言描述逻辑函数的方法将在后面做专门介绍。

#### 一、逻辑真值表

将输入变量所有的取值下对应的输出值找出来,列成表格,即可得到真值表。

仍以图 2.5.1 所示的举重裁判电路为例,根据电路的工作原理不难看出,只有  $A=1$ ,同时  $B$ 、 $C$  至少有一个为 1 时  $Y$  才等于 1,于是可列出图 2.5.1 所示电路的真值表,见表 2.5.1。

表 2.5.1 图 2.5.1 所示电路的真值表

| 输入  |     |     | 输出  |

|-----|-----|-----|-----|

| $A$ | $B$ | $C$ | $Y$ |

| 0   | 0   | 0   | 0   |

| 0   | 0   | 1   | 0   |

| 0   | 1   | 0   | 0   |

续表

| 输入  |     |     | 输出<br>$Y$ |

|-----|-----|-----|-----------|

| $A$ | $B$ | $C$ |           |

| 0   | 1   | 1   | 0         |

| 1   | 0   | 0   | 0         |

| 1   | 0   | 1   | 1         |

| 1   | 1   | 0   | 1         |

| 1   | 1   | 1   | 1         |

## 二、逻辑函数式

将输出与输入之间的逻辑关系写成与、或、非等运算的组合式,即逻辑代数式,就得到了所需的逻辑函数式。

在图 2.5.1 所示的电路中,根据对电路功能的要求和与、或的逻辑定义,“ $B$  和  $C$  中至少有一个合上”可以表示为  $(B+C)$ ,“同时还要求合上  $A$ ”,则应写作  $A \cdot (B+C)$ 。因此得到输出的逻辑函数式为

$$Y = A(B+C) \quad (2.5.1)$$

## 三、逻辑图

将逻辑函数式中各变量之间的与、或、非等逻辑关系用图形符号表示出来,就可以画出描述函数关系的逻辑图(logic diagram)。

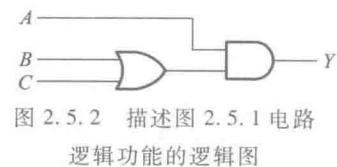

为了画出描述图 2.5.1 电路功能的逻辑图,只要用逻辑运算的图形符号代替式(2.5.1)中的代数运算符号便可得到图 2.5.2 所示的逻辑图。

图 2.5.2 描述图 2.5.1 电路

逻辑功能的逻辑图

## 四、波形图

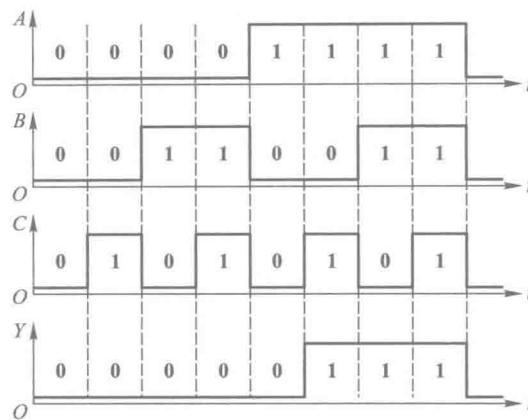

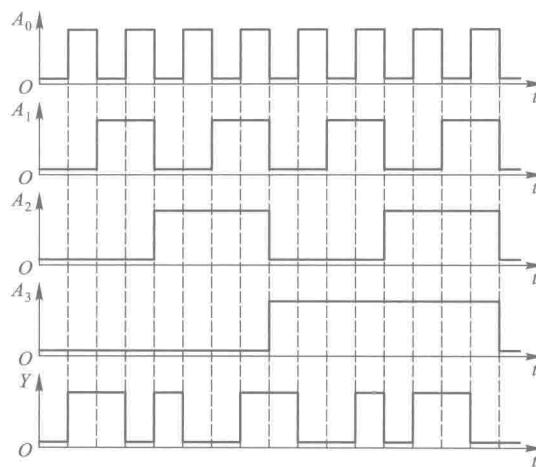

如果将逻辑函数输入变量每一种可能出现的取值与对应的输出值按时间顺序依次排列起来,就得到了描述该逻辑函数的波形图。这种波形图(waveform)也称为时序图(timing diagram)。在逻辑分析仪和一些计算机仿真工具中,经常以这种波形图的形式给出分析结果。此外,也可以通过实验观察这些波形图,以检验实际逻辑电路的功能是否正确。

如果用波形图来描述式(2.5.1)的逻辑函数,则只需将表 2.5.1 给出的输入变量与对应的输出变量取值依时间顺序排列起来,就可以得到所要的波形图了(如图 2.5.3 所示)。

## 五、各种描述方法间的相互转换

从上面的讨论中可以看到,这几种描述方式各具有不同的特点。因此,在实际应用中,需要选择一种最合适的方式来描述所讨论的逻辑函数。当讨论的逻辑函数不是用我们所希望的描述方式给出时,就必须将给出的描述方式转换成我们所需要的描述方式。

图 2.5.3 描述图 2.5.1 电路逻辑功能的波形图

既然同一个逻辑函数可以用多种不同的方法描述,那么这几种方法之间必能相互转换。

### 1. 真值表与逻辑函数式的相互转换

首先讨论从真值表得到逻辑函数式的方法。为了便于理解转换的原理,先来讨论下面一个具体的例子。

**【例 2.5.1】** 已知一个奇偶判别函数的真值表如表 2.5.2 所示,试写出它的逻辑函数式。

表 2.5.2 例 2.5.1 的函数真值表

| A | B | C |  | Y                                        |

|---|---|---|--|------------------------------------------|

| 0 | 0 | 0 |  | $1 \cdots \cdots \rightarrow A'B'C' = 1$ |

| 0 | 0 | 1 |  | 0                                        |

| 0 | 1 | 0 |  | 0                                        |

| 0 | 1 | 1 |  | $1 \cdots \cdots \rightarrow A'BC = 1$   |

| 1 | 0 | 0 |  | 0                                        |

| 1 | 0 | 1 |  | $1 \cdots \cdots \rightarrow AB'C = 1$   |

| 1 | 1 | 0 |  | $1 \cdots \cdots \rightarrow ABC' = 1$   |

| 1 | 1 | 1 |  | 0                                        |

解: 由真值表可见,只有当  $A$ 、 $B$ 、 $C$  三个输入变量中两个同时为 1 或三个同为 0 时,  $Y$  才为 1。因此,在输入变量取值为以下四种情况时,  $Y$  将等于 1:

$$A = 0, B = 0, C = 0$$

$$A = 0, B = 1, C = 1$$

$$A = 1, B = 0, C = 1$$

$$A = 1, B = 1, C = 0$$

而当  $A = 0, B = 0, C = 0$  时,必然使乘积项  $A'B'C' = 1$ ;当  $A = 0, B = 1, C = 1$  时,必然使乘积项  $A'BC = 1$ ;当  $A = 1, B = 0, C = 1$  时,必然使乘积项  $AB'C = 1$ ;当  $A = 1, B = 1, C = 0$  时,必然使  $ABC' = 1$ ,因此  $Y$  的逻辑函数应当等于这四个乘积项之和,即

$$Y = A'B'C' + A'BC + AB'C + ABC'$$

通过例 2.5.1 可以总结出由真值表写出逻辑函数式的一般方法,这就是:

① 找出真值表中使逻辑函数  $Y=1$  的那些输入变量取值的组合。

② 每组输入变量取值的组合对应一个乘积项,其中取值为 1 的写入原变量,取值为 0 的写入反变量。

③ 将这些乘积项相加,即得  $Y$  的逻辑函数式。

由逻辑式列出真值表就更简单了。这时只需将输入变量取值的所有组合状态逐一代入逻辑式求出函数值,列成表,即可得到真值表。

**【例 2.5.2】** 已知逻辑函数  $Y=A+B'C+A'BC'$ ,求它对应的真值表。

解: 将  $A$ 、 $B$ 、 $C$  的各种取值逐一代入  $Y$  式中计算,将计算结果列表,即得表 2.5.3 所示的真值表。初学时为避免差错,可先将  $B'C$ 、 $A'BC'$  两项算出,然后将  $A$ 、 $B'C$  和  $A'BC'$  相加求出  $Y$  的值。

表 2.5.3 例 2.5.2 的真值表

| $A$ | $B$ | $C$ | $B'C$ | $A'BC'$ | $Y$ |

|-----|-----|-----|-------|---------|-----|

| 0   | 0   | 0   | 0     | 0       | 0   |

| 0   | 0   | 1   | 1     | 0       | 1   |

| 0   | 1   | 0   | 0     | 1       | 1   |

| 0   | 1   | 1   | 0     | 0       | 0   |

| 1   | 0   | 0   | 0     | 0       | 1   |

| 1   | 0   | 1   | 1     | 0       | 1   |

| 1   | 1   | 0   | 0     | 0       | 1   |

| 1   | 1   | 1   | 0     | 0       | 1   |

## 2. 逻辑函数式与逻辑图的相互转换

从给定的逻辑函数式转换为相应的逻辑图时,只要用逻辑图形符号代替逻辑函数式中的逻辑运算符号并按运算优先顺序将它们连接起来,就可以得到所求的逻辑图了。

而在从给定的逻辑图转换为对应的逻辑函数式时,只要从逻辑图的输入端到输出端逐级写出每个图形符号的输出逻辑式,就可以在输出端得到所求的逻辑函数式了。

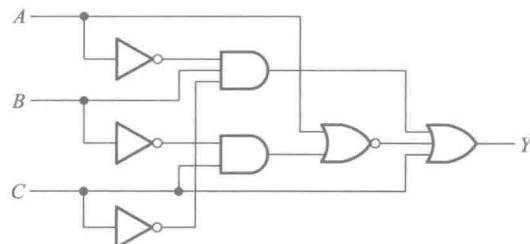

**【例 2.5.3】** 已知逻辑函数为  $Y=(A+B'C)'+A'BC'+C$ ,画出其对应的逻辑图。

解: 将式中所有的与、或、非运算符号用图形符号代替,并依据运算优先顺序将这些图形符号连接起来,就得到了图 2.5.4 所示的逻辑图。

图 2.5.4 例 2.5.3 的逻辑图

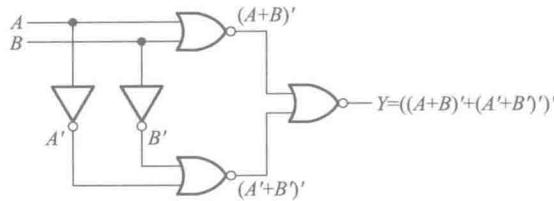

**【例 2.5.4】** 已知函数的逻辑图如图 2.5.5 所示, 试求它的逻辑函数式。

图 2.5.5 例 2.5.4 的逻辑图

解：从输入端  $A$ 、 $B$  开始逐个写出每个图形符号输出端的逻辑式, 得到  $Y=((A+B)'+(A'+B'))'$ 。将该式变换后得到

$$\begin{aligned} Y &= ((A+B)'+(A'+B'))' = (A+B)(A'+B') \\ &= AB' + A'B = A \oplus B \end{aligned}$$

可见, 输出  $Y$  和  $A$ 、 $B$  间是异或逻辑关系。

### 3. 波形图与真值表的相互转换

在从已知的逻辑函数波形图求对应的真值表时, 首先需要从波形图上找出每个时间段里输入变量与函数输出的取值, 然后将这些输入、输出取值对应列表, 就得到了所求的真值表。

在将真值表转换为波形图时, 只需将真值表中所有的输入变量与对应的输出变量取值依次排列画成以时间为横轴的波形, 就得到了所求的波形图, 如我们前面已经做过的那样。

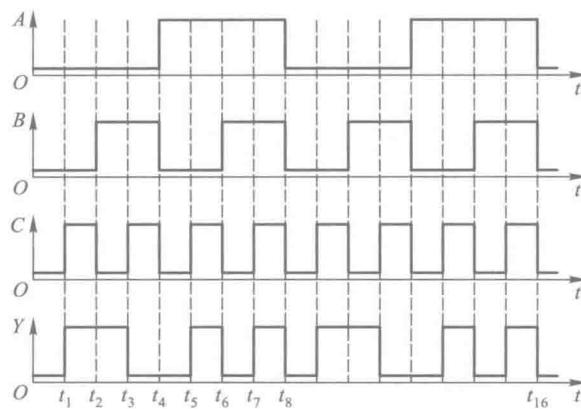

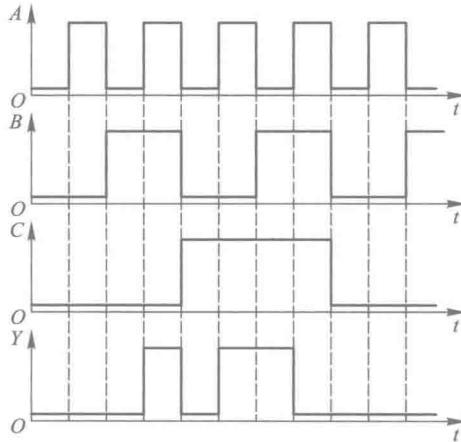

**【例 2.5.5】** 已知逻辑函数  $Y$  的波形图如图 2.5.6 所示, 试求该逻辑函数的真值表。

图 2.5.6 例 2.5.5 的波形图

解：从  $Y$  的波形图上可以看出, 在  $0 \sim t_8$  时间区间里输入变量  $A$ 、 $B$ 、 $C$  所有可能的取值组合均已出现了, 而且  $t_8 \sim t_{16}$  区间的波形只不过是  $0 \sim t_8$  区间波形的重复。因此, 只要将  $0 \sim t_8$  区间每个时间段里  $A$ 、 $B$ 、 $C$  与  $Y$  的取值对应列表, 即可得表 2.5.4 所示的真值表。

表 2.5.4 例 2.5.5 的真值表

| A | B | C | Y |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

### 2.5.3 逻辑函数的两种标准形式

在讲述逻辑函数的标准形式之前,先介绍一下最小项和最大项的概念,然后再介绍逻辑函数的“最小项之和”及“最大项之积”这两种标准形式。

#### 一、最小项和最大项

##### 1. 最小项

在  $n$  变量逻辑函数中,若  $m$  为包含  $n$  个因子的乘积项,而且这  $n$  个变量均以原变量或反变量的形式在  $m$  中出现一次,则称  $m$  为该组变量的最小项。

例如, $A$ 、 $B$ 、 $C$  三个变量的最小项有  $A'B'C'$ 、 $A'B'C$ 、 $A'BC'$ 、 $A'BC$ 、 $AB'C'$ 、 $AB'C$ 、 $ABC'$ 、 $ABC$  共 8 个(即  $2^3$  个)。 $n$  变量的最小项应有  $2^n$  个。

输入变量的每一组取值都使一个对应的最小项的值等于 1。例如,在三变量  $A$ 、 $B$ 、 $C$  的最小项中,当  $A=1$ 、 $B=0$ 、 $C=1$  时, $AB'C=1$ 。如果把  $AB'C$  的取值 101 看作一个二进制数,那么它所表示的十进制数就是 5。为了今后使用的方便,将  $AB'C$  这个最小项记作  $m_5$ 。按照这一约定,就得到了三变量最小项的编号表,如表 2.5.5 所示。

表 2.5.5 三变量最小项的编号表

| 最小项        | 使最小项为 1 的变量取值 |   |   | 对应的十进制数 | 编号    |

|------------|---------------|---|---|---------|-------|

|            | A             | B | C |         |       |

| $A' B' C'$ | 0             | 0 | 0 | 0       | $m_0$ |

| $A' B' C$  | 0             | 0 | 1 | 1       | $m_1$ |

| $A' B C'$  | 0             | 1 | 0 | 2       | $m_2$ |

| $A' B C$   | 0             | 1 | 1 | 3       | $m_3$ |

| $A B' C'$  | 1             | 0 | 0 | 4       | $m_4$ |

| $A B' C$   | 1             | 0 | 1 | 5       | $m_5$ |

| $A B C'$   | 1             | 1 | 0 | 6       | $m_6$ |

| $A B C$    | 1             | 1 | 1 | 7       | $m_7$ |

根据同样的道理,我们将  $A, B, C, D$  这 4 个变量的 16 个最小项记作  $m_0 \sim m_{15}$ 。

从最小项的定义出发可以证明它具有如下的重要性质:

- ① 在输入变量的任何取值下必有一个最小项,而且仅有一个最小项的值为 1。

- ② 全体最小项之和为 1。

- ③ 任意两个最小项的乘积为 0。

- ④ 具有相邻性的两个最小项之和可以合并成一项并消去一对因子。

若两个最小项只有一个因子不同,则称这两个最小项具有相邻性。例如, $A'BC'$  和  $ABC'$  两个最小项仅第一个因子不同,所以它们具有相邻性。这两个最小项相加时定能合并成一项并将一对不同的因子消去

$$A'BC' + ABC' = (A' + A)BC' = BC'$$

### \* 2. 最大项

在  $n$  变量逻辑函数中,若  $M$  为  $n$  个变量之和,而且这  $n$  个变量均以原变量或反变量的形式在  $M$  中出现一次,则称  $M$  为该组变量的最大项。

例如,三变量  $A, B, C$  的最大项有  $(A'+B'+C')$ 、 $(A'+B'+C)$ 、 $(A'+B+C')$ 、 $(A'+B+C)$ 、 $(A+B'+C')$ 、 $(A+B'+C)$ 、 $(A+B+C')$ 、 $(A+B+C)$  共 8 个(即  $2^3$  个)。对于  $n$  个变量则有  $2^n$  个最大项。可见,  $n$  变量的最大项数目和最小项数目是相等的。

输入变量的每一组取值都使一个对应的最大项的值为 0。例如,在三变量  $A, B, C$  的最大项中,当  $A=1, B=0, C=1$  时,  $(A'+B+C')=0$ 。若将使最大项为 0 的  $ABC$  取值视为一个二进制数,并以其对应的十进制数给最大项编号,则  $(A'+B+C')$  可记作  $M_5$ 。由此得到的三变量最大项编号表,如表 2.5.6 所示。

表 2.5.6 三变量最大项的编号表

| 最大项        | 使最大项为 0 的变量取值 |   |   | 对应的十进制数 | 编号    |

|------------|---------------|---|---|---------|-------|

|            | A             | B | C |         |       |

| $A+B+C$    | 0             | 0 | 0 | 0       | $M_0$ |

| $A+B+C'$   | 0             | 0 | 1 | 1       | $M_1$ |

| $A+B'+C$   | 0             | 1 | 0 | 2       | $M_2$ |

| $A+B'+C'$  | 0             | 1 | 1 | 3       | $M_3$ |

| $A'+B+C$   | 1             | 0 | 0 | 4       | $M_4$ |

| $A'+B+C'$  | 1             | 0 | 1 | 5       | $M_5$ |

| $A'+B'+C$  | 1             | 1 | 0 | 6       | $M_6$ |

| $A'+B'+C'$ | 1             | 1 | 1 | 7       | $M_7$ |

根据最大项的定义同样也可以得到它的主要性质,这就是:

- ① 在输入变量的任何取值下必有一个最大项,而且只有一个最大项的值为 0。

- ② 全体最大项之积为 0。

- ③ 任意两个最大项之和为 1。

④ 只有一个变量不同的两个最大项的乘积等于各相同变量之和。

如果将表 2.5.5 和表 2.5.6 加以对比则可发现，最大项和最小项之间存在如下关系

$$M_i = m'_i \quad (2.5.2)$$

例如， $m_0 = A'B'C'$ ，则  $m'_0 = (A'B'C')' = A+B+C = M_0$

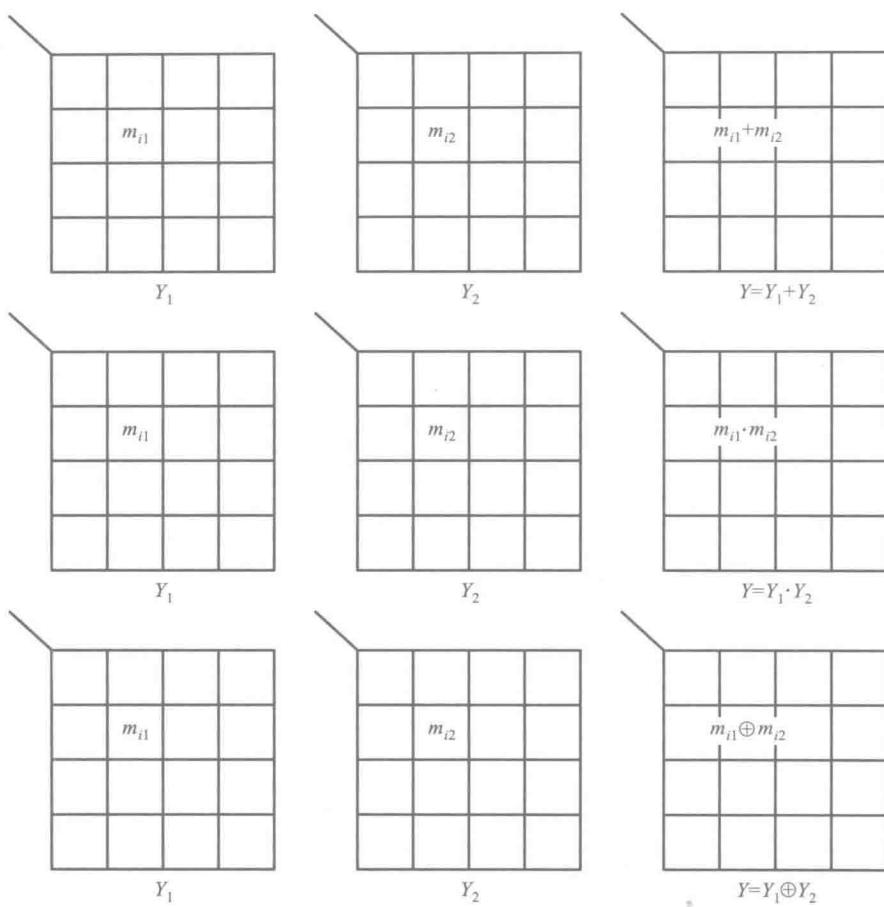

## 二、逻辑函数的最小项之和形式

首先将给定的逻辑函数式化为若干乘积项之和的形式，亦称“积之和”(sum of products，简称 SOP)形式。然后，再利用基本公式  $A+A'=1$  将每个乘积项中缺少的因子补全，这样就可以将与或的形式化为最小项之和的标准形式。这种标准形式在逻辑函数的化简以及计算机辅助分析和设计中得到了广泛的应用。

例如，给定逻辑函数为

$$Y=ABC'+BC$$

则可化为

$$Y=ABC'+(A+A')BC=ABC'+ABC+A'BC=m_3+m_6+m_7$$

或写作

$$Y(A,B,C)=\sum m(3,6,7)$$

**【例 2.5.6】** 将逻辑函数  $Y=AB'C'D+A'CD+AC$  展开为最小项之和的形式。

$$\begin{aligned} \text{解: } Y &= AB'C'D+A'(B+B')CD+A(B+B')C \\ &= AB'C'D+A'BCD+A'B'CD+ABC(D+D')+AB'C(D+D') \\ &= AB'C'D+A'BCD+A'B'CD+ABCD+ABCD'+AB'CD+AB'CD' \end{aligned}$$

或写作

$$Y(A,B,C,D)=\sum m(3,7,9,10,11,14,15)$$

## \* 三、逻辑函数的最大项之积形式

利用逻辑代数的基本公式和定理，首先我们一定能把任何一个逻辑函数式化成若干多项式相乘的或与形式(也称“和之积”形式)。然后再利用基本公式  $AA'=0$  将每个多项式中缺少的变量补齐，就可以将函数式的或与形式化成最大项之积的形式了。

**【例 2.5.7】** 将逻辑函数  $Y=A'B+AC$  化为最大项之积的形式。

解：首先可以利用基本公式  $A+BC=(A+B)(A+C)$  将  $Y$  化成或与形式

$$\begin{aligned} Y &= A'B+AC \\ &= (A'B+A)(A'B+C) \\ &= (A+B)(A'+C)(B+C) \end{aligned}$$

然后在第一个括号内加入一项  $CC'$ ，在第二个括号内加入  $BB'$ ，在第三个括号内加入  $AA'$ ，于是得到

$$\begin{aligned} Y &= (A+B+CC')(A'+BB'+C)(AA'+B+C) \\ &= (A+B+C)(A+B+C')(A'+B+C)(A'+B'+C) \end{aligned}$$

或写作

$$Y(A,B,C,D)=\prod M(0,1,4,6)$$

## 复习思考题

R2.5.1 逻辑函数的描述方法有哪几种？你能把由任何一种描述方法给出的逻辑函数转换为由其他任何一种描述方法表示的逻辑函数吗？

R2.5.2 在逻辑函数的真值表和波形图中，任意改变各组输入和输出取值的排列顺序对函数有无影响？

## 2.6 逻辑函数的化简方法

### 2.6.1 公式化简法

在进行逻辑运算时常常会看到，同一个逻辑函数可以写成不同的逻辑式，而这些逻辑式的繁简程度又相差甚远。逻辑式越是简单，它所表示的逻辑关系越明显，同时也有利于用最少的电子器件实现这个逻辑函数。因此，经常需要通过化简的手段找出逻辑函数的最简形式。

例如，有两个逻辑函数

$$Y = ABC + B'C + ACD \quad (2.6.1)$$

$$Y = AC + B'C \quad (2.6.2)$$

将它们的真值表分别列出后即可见到，它们是同一个逻辑函数。显然，下式比上式简单得多。

在与或逻辑函数式中，若其中包含的乘积项已经最少，而且每个乘积项里的因子也不能再减少时，则称此逻辑函数式为最简形式。对与或逻辑式最简形式的定义对其他形式的逻辑式同样也适用，即函数式中相加的乘积项不能再减少，而且每项中相乘的因子不能再减少时，则函数式为最简形式。

化简逻辑函数的目的就是要消去多余的乘积项和每个乘积项中多余的因子，以得到逻辑函数式的最简形式。常用的化简方法有公式化简法、卡诺图化简法以及适用于编制计算机辅助分析程序的Q-M法等。

公式化简法的原理就是反复使用逻辑代数的基本公式和常用公式消去函数式中多余的乘积项和多余的因子，以求得函数式的最简形式。

公式化简法没有固定的步骤。现将经常使用的方法归纳如下。

#### 一、并项法

利用表2.3.3中的公式  $AB+AB'=A$  可以将两项合并为一项，并消去  $B$  和  $B'$  这一对因子。而且，根据代入定理可知， $A$  和  $B$  均可以是任何复杂的逻辑式。

**【例2.6.1】** 试用并项法化简下列逻辑函数

$$Y_1 = A(B'CD)' + AB'CD$$

$$Y_2 = AB' + ACD + A'B' + A'CD$$

$$Y_3 = A'BC' + AC' + B'C'$$

$$Y_4 = BC'D + BCD' + BC'D' + BCD$$

解：

$$Y_1 = A((B'CD)' + B'CD) = A$$

$$Y_2 = A(B' + CD) + A'(B' + CD) = B' + CD$$

$$Y_3 = A'BC' + (A+B')C' = (A'B)C' + (A'B')C' = C'$$

$$Y_4 = B(C'D + CD') + B(C'D' + CD)$$

$$= B(C \oplus D) + B(C \oplus D)' = B$$

## 二、吸收法

利用表 2.3.3 中的公式  $A+AB=A$  可将  $AB$  项消去。 $A$  和  $B$  同样也可以是任何一个复杂的逻辑式。

**【例 2.6.2】** 试用吸收法化简下列逻辑函数

$$Y_1 = ((A'B)' + C)ABD + AD$$

$$Y_2 = AB + ABC' + ABD + AB(C' + D')$$

$$Y_3 = A + (A'(BC)')'(A' + (B'C' + D)') + BC$$

解：

$$Y_1 = ((A'B)' + C)B \cdot AD + AD = AD$$

$$Y_2 = AB + AB(C' + D + (C' + D')) = AB$$

$$Y_3 = (A + BC) + (A + BC)(A' + (B'C' + D)') = A + BC$$

## 三、消项法

利用表 2.3.3 中的公式  $AB+A'C+BC=AB+A'C$  及  $AB+A'C+BCD=AB+A'C$  将  $BC$  或  $BCD$  项消去。其中  $A, B, C, D$  均可以是任何复杂的逻辑式。

**【例 2.6.3】** 用消项法化简下列逻辑函数

$$Y_1 = AC + AB' + (B+C)'$$

$$Y_2 = AB'CD' + (AB')'E + A'CD'E$$

$$Y_3 = A'B'C + ABC + A'BD' + AB'D' + A'BCD' + BCD'E'$$

解：

$$Y_1 = AC + AB' + B'C' = AC + B'C'$$

$$Y_2 = (AB')CD' + (AB')'E + (CD')(E)A' \\ = AB'CD' + (AB')'E$$

$$Y_3 = (A'B'+AB)C + (A'B+AB')D' + BCD'(A'+E') \\ = (A \oplus B)'C + (A \oplus B)D' + CD'(B(A'+E')) \\ = (A \oplus B)'C + (A \oplus B)D'$$

## 四、消因子法

利用表 2.3.3 中的公式  $A+A'B=A+B$  可将  $A'B$  中的  $A'$  消去。 $A, B$  均可以是任何复杂的逻辑式。

**【例 2.6.4】** 试利用消因子法化简下列逻辑函数

$$Y_1 = B' + ABC$$

$$Y_2 = AB' + B + A'B$$

解：

$$\begin{aligned}

Y_3 &= AC + A'D + C'D \\

Y_1 &= B' + ABC = B' + AC \\

Y_2 &= AB' + B + A'B = A + B + A'B = A + B \\

Y_3 &= AC + A'D + C'D = AC + (A' + C')D = AC + (AC)'D \\

&= AC + D

\end{aligned}$$

### 五、配项法

① 根据基本公式中的  $A+A=A$  可以在逻辑函数式中重复写入某一项，有时能获得更加简单的化简结果。

**【例 2.6.5】** 试化简逻辑函数  $Y = A'BC' + A'BC + ABC$ 。

解：若在式中重复写入  $A'BC$ ，则可得到

$$\begin{aligned}

Y &= (A'BC' + A'BC) + (A'BC + ABC) \\

&= A'B(C+C') + BC(A+A') \\

&= A'B + BC

\end{aligned}$$

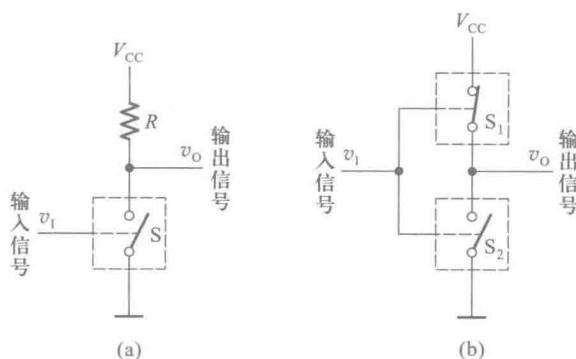

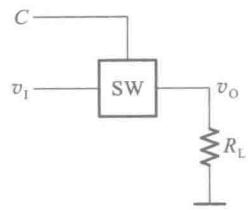

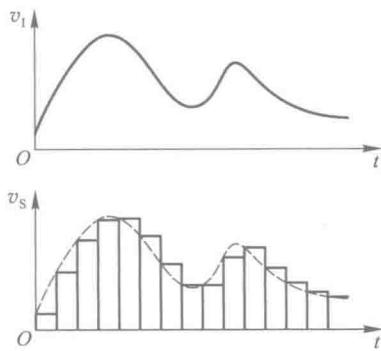

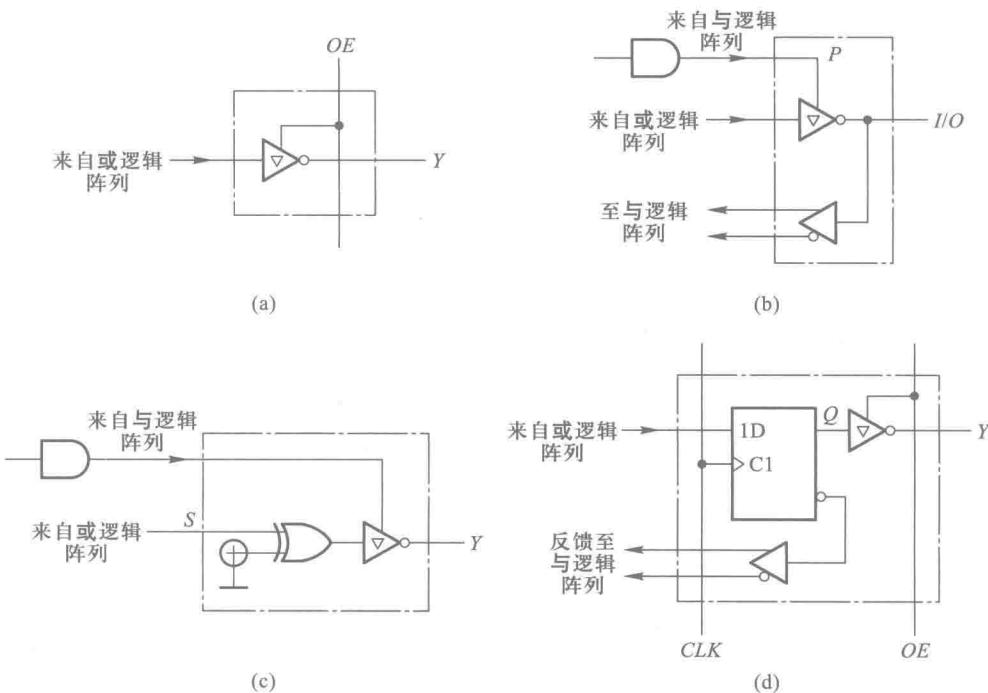

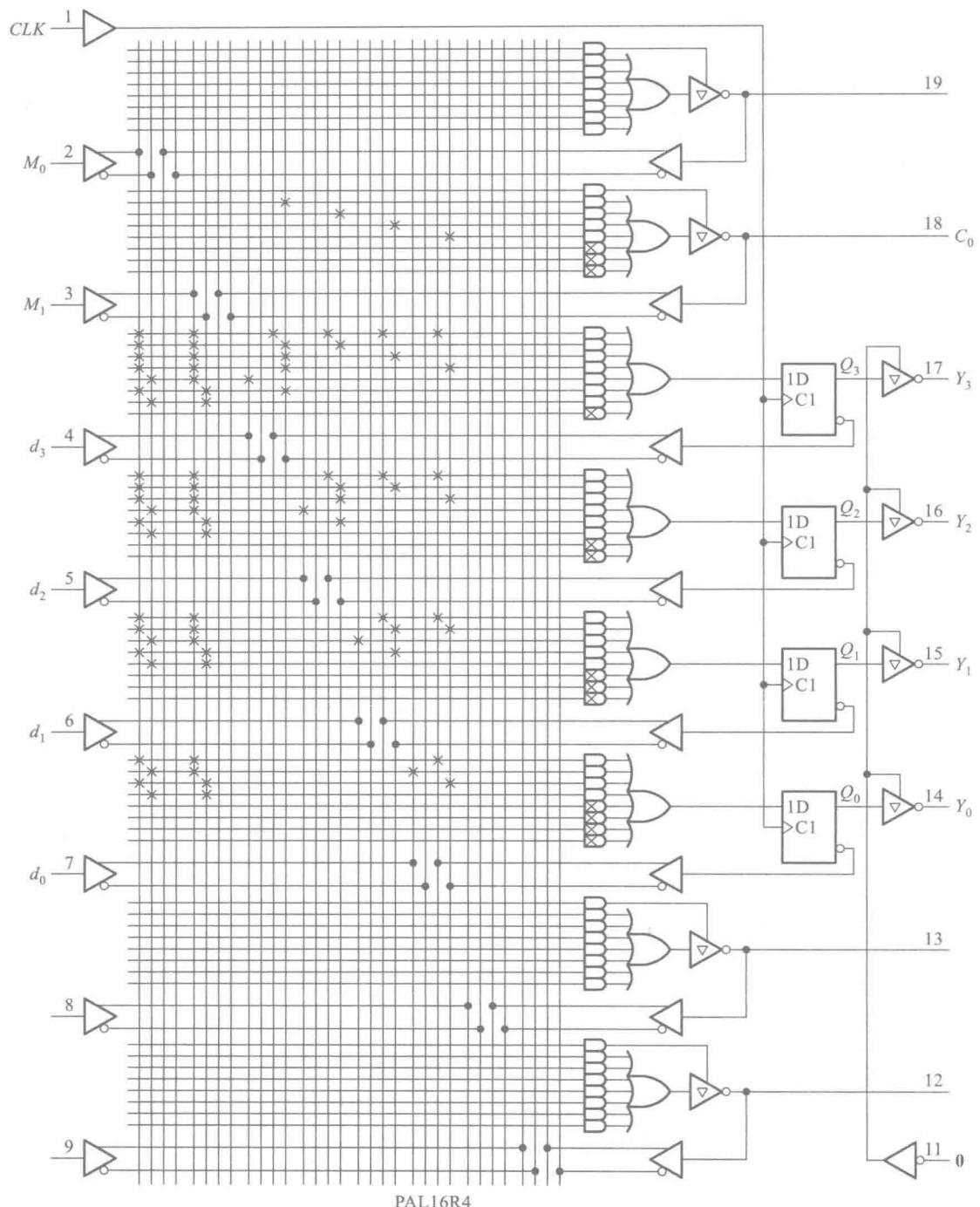

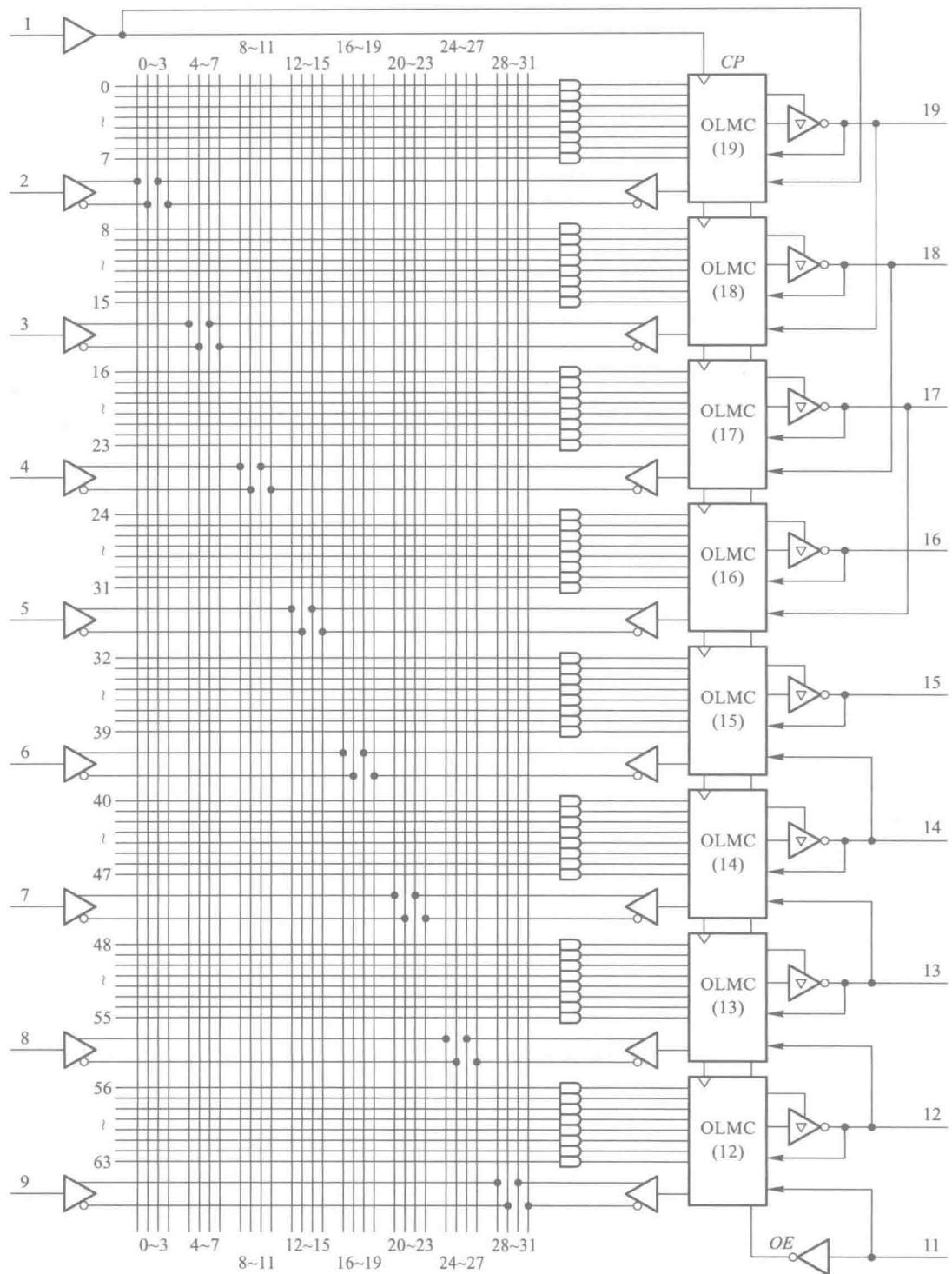

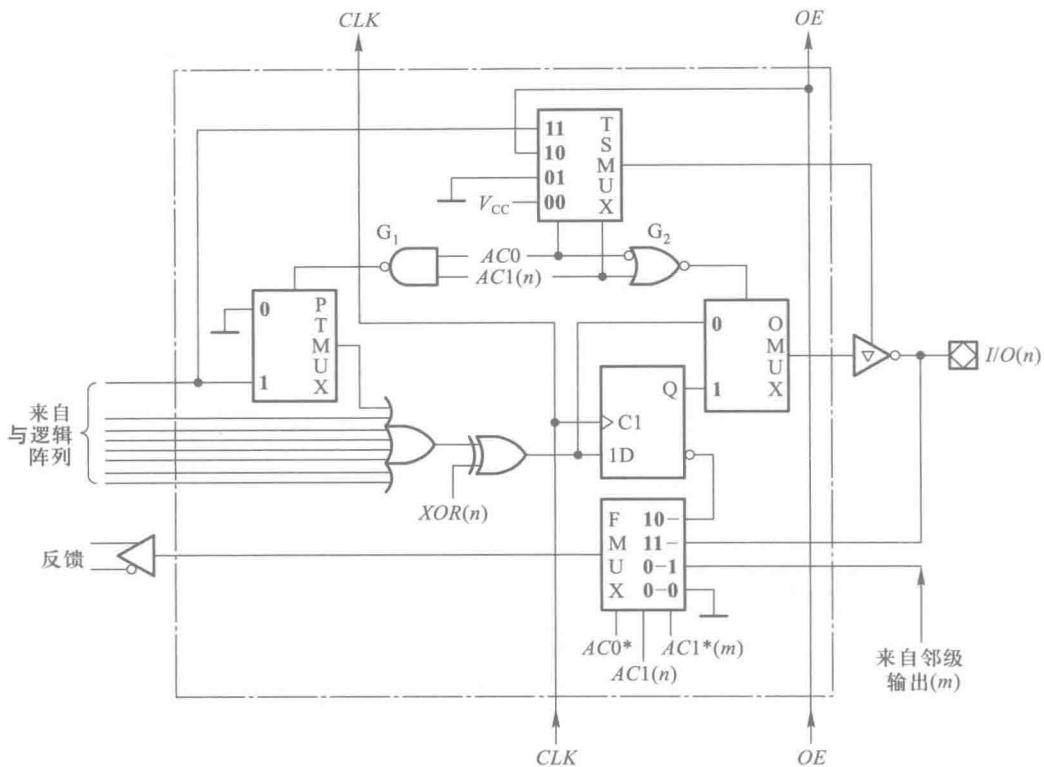

② 根据基本公式中的  $A+A'=1$  可以在函数式中的某一项上乘以  $(A+A')$ ，然后拆成两项分别与其他项合并，有时能得到更加简单的化简结果。